# System description

## **ABB Procontic T300**

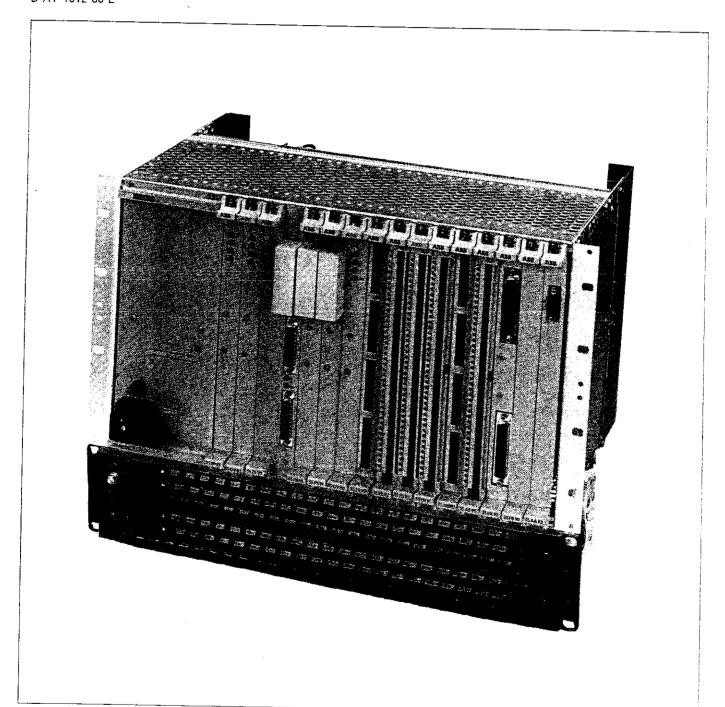

Multiprocessor Control System

Hardware

Order number GATS 1315 01 R2002 part 2 replaces Publication number D AT 1612 88 E

#### Regulations

## Regulations Concerning the Setting up of Installations

Apart from the basic "Regulations for the Setting up of Power Units" VDE\* 0100 and for "The Rating of Creepage Paths and Air Gaps" VDE 0110 the regulations "The Equipment of Power Units with Electrical Components" VDE 0160 in connection with VDE 0660, part 500, have to be taken into due consideration. Further attention has to be paid to VDE 0113 in case of the control of working and processing machines. If operating elements are to be arranged near shock—hazard parts with protection against electrical shock, VDE 0106, part 100, is relevant.

The user has to ensure that the units as well as the associated components have to be installed according to these regulations. Respectively valid safety regulations, e.g. regulation for the prevention of accidents and the law concerning technical working material, are valid for machines and units connected as well.

ABB Procontic units have been built according to VDE regulation 0160. The protection against direct touching as demanded by chapter 5.5.1 of this VDE regulation has to be satisfied by the user, e.g. at installing of switch cabinet.

ABB Procontic units have been designed for operation according to insulation class A of VDE 0110. If considerable polution is expected during operations, the units have to be installed in housings of the respective kind of protection.

\* VDE stands for "Association of German Electrical Engineers".

Note: Please observe the national regulations for the installation of electrical equipments, which are valid in your country.

ABB Schalt- und Steuerungstechnik GmbH

### **Contents**

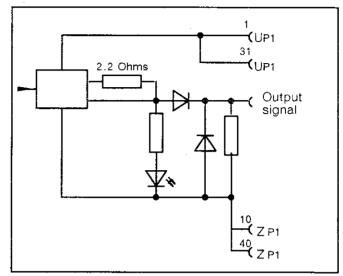

| 1    | General part                                                  | 7                   | Memory cards                             |                    |

|------|---------------------------------------------------------------|---------------------|------------------------------------------|--------------------|

| 1.1  | System overview 1.                                            |                     | ·                                        |                    |

| 1.2  | •                                                             | !                   |                                          |                    |

| 1.3  | Description of the MPST                                       | ,- ,<br>7.2         | 35 PS 91 R12, R13 and R14                | 7.1-               |

|      |                                                               | 7.2<br>1- 2         | Memory card 35 PS 91 R22                 | 7.2-               |

| 1.4  |                                                               |                     | DIO services in                          |                    |

| 1.5  |                                                               | ı_ /I <b>Ö</b>      | PLC central units                        |                    |

| 1.6  | Ambient conditions 1.1                                        | - 4 8.1<br> - 5     | PLC central unit                         |                    |

|      |                                                               | 8.2                 | 35 ZE 93 R301                            | 8.1-               |

| ^    | Page and the t                                                | 0.2                 | PLC central unit<br>35 ZE 94 R101        | • •                |

| 2    | Fans and subracks                                             |                     | 33 2L 34 NIOI                            | 8.2- 1             |

| 2.1  |                                                               | - 1<br>9            | CNO paratual costs                       |                    |

| 2.2  | Subrack 35 GS 91 R1 with power                                |                     | CNC central units                        |                    |

|      | supply unit 35 NE 90 R1 for                                   | 9.1                 | Positioning unit 35 GV 80 R101           | 9.1- 1             |

| 2.3  | 220 V AC voltage supply 2.2<br>Subrack 35 GS 93 R1 with power | 9.2<br>9.3          |                                          | 9.2- 1             |

| ۷.5  | supply unit 35 NE 93 R1 for                                   | 5.3                 | Central control unit 35 ZS 86 R101       |                    |

|      | 04 14 50                                                      | - 1                 | 35 25 66 HIU1                            | 9.3 1              |

|      | z Do tomago supply 2.3                                        |                     | Andata .                                 |                    |

|      |                                                               | 10                  | Axis units                               |                    |

| 3    | Power supply units                                            | 10.                 | gg modulo                                |                    |

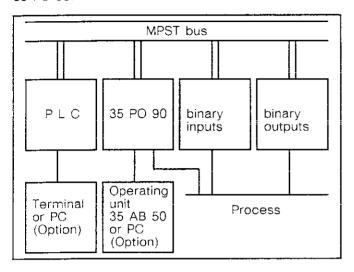

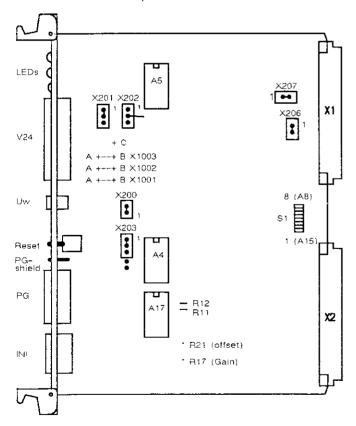

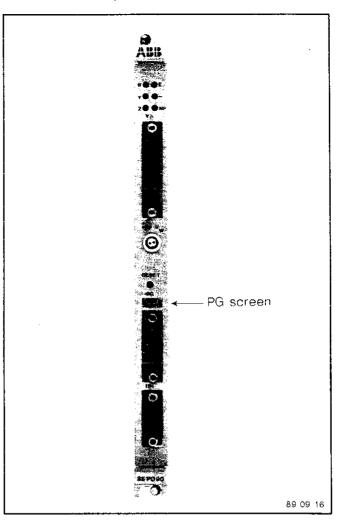

| 3.1  | Power supply unit 35 NE 93 R1                                 | 10.2                | 35 PO 90 R101                            | 10.1- 1            |

|      | for 24 V DC 3.1                                               |                     | 02 712 02 717, 718                       | 10.2- 1            |

|      |                                                               | 10.0                | moremental input 35 AE 92 Rb             | 10.3- 1            |

| 4    | Bus coupler units                                             | 11                  | IR central units                         |                    |

| 4.1  | Bus coupler unit 35 EK 90 R1 for                              | 11.1                |                                          |                    |

|      | the basic subrack 4.1                                         | _ 1                 | 35 IR 93 R101                            | 11.1- 1            |

| 4.2  | Bus coupler unit 35 EK 91 R1 for                              | •                   |                                          |                    |

|      | the extention subrack 4.2                                     | - 1 <b>12</b>       | Opto-electrical measuring                |                    |

| 4.3  | Connecting cable 35 SK 96 R1                                  |                     | and sensor system, OMS-F                 |                    |

|      | for bus coupler 4.3                                           | - 1 12.1            |                                          |                    |

| 4.4  | Example of a bus coupling with                                | 12.2                |                                          | 12.1- 1            |

|      | the bus coupler units 35 EK 90,                               |                     | 35 IV 90 R1                              | 12 2- 1            |

|      | 35 EK 91 and the connecting cable                             |                     |                                          | 12.2               |

|      | 35 SK 96 4.4-                                                 | <sup>- 1</sup> 13   | Binary input units                       |                    |

|      |                                                               | 13:1                |                                          |                    |

| 5    | Processor cards                                               | ,0,1                | 35 EB 90 R1                              | 13.1- 1            |

| 5.1  | Processor card                                                | 13.2                |                                          | 13.2- 1            |

|      | 35 ZP 93 R11, R21 5.1-                                        | <sub>- 1</sub> 13.3 |                                          | ,0.2               |

| 5.2  | Processor card                                                | ,                   | 35 EB 91 R1 and R2                       | 13.3- 1            |

|      | 35 ZP 93 R31, R41 5.2                                         | - 1 13.4            | <b>y</b> 1= = = +                        |                    |

|      |                                                               |                     | 35 EB 92 R1 and R2                       | 13.4- 1            |

| 6    | Interfaces                                                    | 14                  | Analog input wite                        |                    |

| 5.1  | Interface                                                     |                     | Analog input units                       |                    |

| V. 1 | 35 DS 90 R20 6.1-                                             | 14.1                |                                          |                    |

| 5.2  | Interface                                                     | - ı<br>14.2         | analog input units                       | 14.1- 1            |

| _    | 35 DS 91 R1 6.2-                                              |                     |                                          | 14.2- 1            |

| 3.3  | Interface                                                     | 14.3                | A (                                      | 14.3- 1            |

|      | 35 DS 91 R2, R3 6.3-                                          |                     | 9 11 11 11 11 11 11 11 11 11 11 11 11 11 | 14.4- 1<br>14.5- 1 |

|      |                                                               |                     |                                          | 1 T.J- 1           |

| 15   | Binary output units               | 18   | Couplers                         |         |

|------|-----------------------------------|------|----------------------------------|---------|

| 15.1 | Binary output unit                | 18.1 | Coupler between                  |         |

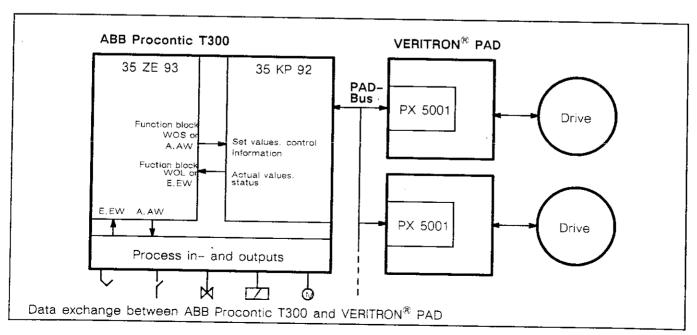

|      | 35 AB 90 R1 15.1- 1               |      | the ABB Procontic T300 and       |         |

| 15.2 | Cables and output modules 15.2- 1 |      | the ABB Procontic field bus ZB10 | o.      |

| 15.3 | Binary output unit                |      | 35 ZB 91 R1                      | 18.1- 1 |

|      | 35 AB 94 R1 15.3- 1               |      |                                  |         |

| 15.4 | Binary output unit                | 19   | Service auxiliary units          |         |

|      | 35 AB 95 R1 15.4- 1               | 19.1 | Bus extension 35 SH 90           | 10.1.1  |

| 15.5 | Binary output unit                | 10.2 | Bus display 35 SH 91             |         |

|      | 35 AB 96 R1 15.5- 1               | 19.3 | Axis simulator 35 SH 94          |         |

| 15.6 | Binary output unit                |      | Axis simulator 55 Ori 54         | 15.5- 1 |

|      | 35 AB 97 R2 15.6- 1               | 20   | Custom sobles                    |         |

|      |                                   | 20   | System cables                    |         |

|      |                                   | 20.1 | Connecting cable 35 SK 93 R1     | 20.1- 1 |

| 16   | Analog output units               | 20.2 | Extension cable                  |         |

|      | _ ·                               |      | 35 SK 93 R11                     | 20.2- 1 |

| 16.1 | Analog output unit                | 20.3 | Connecting cable 35 SK 94        | 20.3- 1 |

|      | 35 AA 92 R2 16.1- 1               | 20.4 | Extension cable                  |         |

|      |                                   |      | 35 SK 95 R1                      |         |

|      |                                   | 20.5 | Connecting cable 35 SK 97        | 20.5- 1 |

| 17   | Communications processors         |      |                                  |         |

| 17.1 | Communications processor          | 21   | Accessories                      |         |

|      | 35 KP 90 R101 17.1- 1             | 21.1 | Dummy cover 35 FB 90             | 21.1- 1 |

| 17.2 | Communications processor          | 21.2 | Front plug 35 ST 90              |         |

|      | 35 KP 91 R101 17.2- 1             | 21.3 | Label strips35 SB 90             |         |

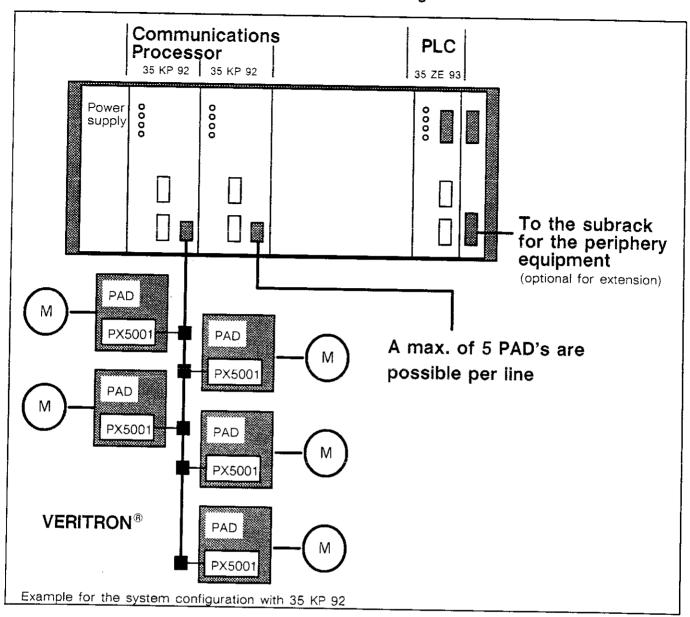

| 17.3 | Communications processor          | 21.4 | Lithium battery 07 LB 20 R1      |         |

|      | 35 KP 92 R101 17.3- 1             | 21.5 | Lithium battery module           |         |

|      |                                   |      |                                  | 04 5 4  |

# 1 General part

This is a description of the system concept, the system structure, the bus signals, the electrical characteristics and the ambient conditions of the ABB Procontic T300.

### Contents, Chapter 1

| <b>1.1</b><br>1.1.1<br>1.1.2 | System overview 1.1- System concept 1.1 Development of the MPST system 1.1 | _ 1 1.3.4<br>1.3.5 | Bus operations                | 1.1- 4<br>1.1- 4<br>1.1- 4 |

|------------------------------|----------------------------------------------------------------------------|--------------------|-------------------------------|----------------------------|

| 1.2                          | System structure 1.1-                                                      | - 1 1.4            | Electrical characteristics .  | 1.1- 4                     |

| 1.2.1                        | Hardware structure 1.1                                                     |                    | Voltage supply                | 1.1- 4                     |

| 1.2.2                        | Software structure 1.1                                                     | _ 2 1.4.2          | Signal levels (bus signals)   | 1.1- 4                     |

|                              |                                                                            | 1.4.3              | Non-specified bus connections | 1.1- 4                     |

| 1.3                          | Description of the MPST parallel bus 1.1-                                  | <sub>- 2</sub> 1.5 | Mechanical structure          | 1.1- 4                     |

| 1.3.1                        | Requirements 1.1                                                           | - 2                |                               |                            |

| 1.3.2                        | Bus signals 1.1                                                            | _ 3 <b>1.6</b>     | Ambient conditions            | 1.1- 5                     |

#### 1.1 System overview

#### 1.1.1 System concept

ABB Procontic T300 is a universal, extendable component system for building up control systems for the entire automation technology. The basis for this is a modular, standardized hard-/software system, which completely exhausts the technological possibilities by using microprocessors and complex periphery switch circuits, on the one hand, and, on the other hand, gives the user sufficient choice in the selection of the system blocks.

The field of application of the ABB Procontic T300 system stretches from processing operating information (programmable controller) via the control of actuators and variable-speed drives through to numerical path creation for separate and linked machines. Control systems for complex applications can be built up with a combination of standard blocks due to the modular structure.

Moreover, the modular concept allows a longer lifetime of the system, since control systems can be constantly kept up-to-date functionally and technologically according to the state of development by retrofits, new function units and new, digital components.

A prerequisite for a modular control system is the division of the control task into greatly independent partial tasks. The possibility of communication between these function units must be given to combine various partial tasks on several function units into an entire control. Since ABB Procontic T300 is designed as a block system, the communication requires clearly defined hardware interfaces but also more importantly software interfaces as a prerequisite, as well as methods to coordinate the function software of the separate blocks, so that the separate units can fulfill the given control task altogether.

The description and determination of the hardware interfaces to the module limits led to the development of a standardized bus system (multiprocessor-based control bus = MPST), which is **independent of the microprocessor** and which enables an effective data exchange between the modules within the system.

The determination of the software includes the definition of a hierarchal software structure as well as of an order method based on this in order to be able to coordinate the sequence of the software of the individual function units. Moreover, interfaces for the exchange of information between the function units were defined, whereby two levels of the exchange of information were considered. On the one hand, interfaces for the exchange of subscriber data were created and, on the

other hand, interfaces for the exchange of information concerning the development of the order method.

#### 1.1.2 Development of the MPST system

The MPST system was developed by the MPST working committee, which was composed of institutes of further education, control manufacturers and machine manufacturers. The development was promoted within the framework of the 3rd data processing program of the BMFT, under the responsibility of the nuclear research company in Karlsruhe (Kernforschungsgesellschaft Karlsruhe).

The activities of the MPST working committee were transferred to the newly founded MPST committee (registered association) (MPST-Kreis e.V.) after the general completion of the development of the MPST concept.

The interface determination in the MPST has appeared as a standard (DIN 66264, to be requested from Beuth Verlag GmbH, Berlin 30), whereby part 1 of this standard describes the parallel bus and part 2 the information interfaces.

#### 1.2 System structure

#### 1.2.1 Hardware structure

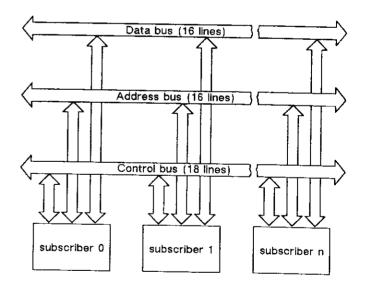

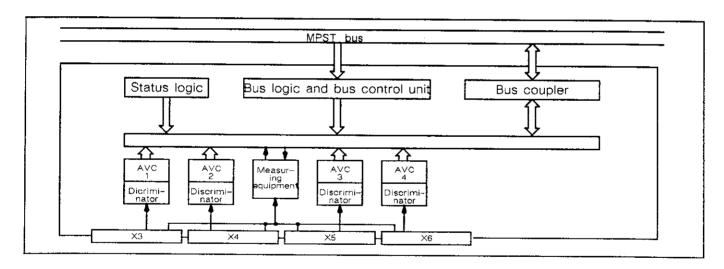

The hardware structure of the modular MPST system, ABB Procontic T300 is based on the MPST parallel bus with data, address and control lines. A subscriber is a function unit which is realized by one or several printed boards. A characteristic of the subscriber is that it can be addressed via the MPST parallel bus.

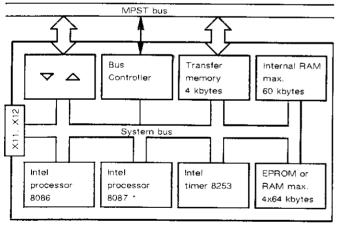

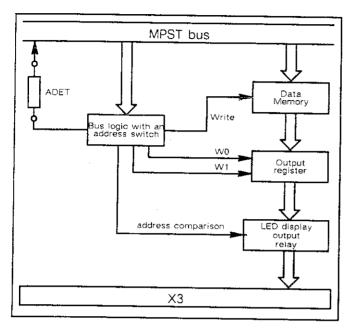

Fig.1-1 Hardware structure

The system distinguishes between active and passive subscribers.

#### Active subscribers

Active subscribers can address other subscribers, like processor units, for example, and exchange data with them. The active subscriber carries out read and write operations with other subscribers independently.

Example: Processor card with PLC software

#### Passive subscribers

A passive subscriber, like an in- or output unit, for example, is addressed by an active subscriber.

Example: Memory card 35 PS 91

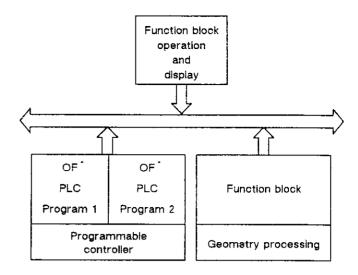

#### 1.2.2 Software structure

If you examine a given control task with functional points in mind, function blocks can first be defined, which undertake a fixed task in the entire system.

Machine control example: Operating and display block, control blocks, diagnosis block, etc.

The distinction between the separate function blocks is chosen, so that **the amount of data** as well as **the frequency** of the exchange of data with other function blocks is kept to a minimum, if possible. Each function block is divided into functions in the next stage (geometry block example: interpolation, position control, override, etc.). The functions can be composed again of general program blocks by using a program library (arithmetic routines, algorithms, code conversion routines, string operations, etc.).

A uniform software interface was created for the communication between the function blocks based on this hierarchal software structure. From the subscriber's point of view, the smallest activity within a function block, which can be recalled, is the orderable function (OF; geometry block example: reference point movement). This function can be compared with the "task" concept. Assigning orders to an OF occurs by filling in control blocks. Since the structure of these control blocks was standardized for the ABB Procontic T300 system, all functions can be addressed and executed in the system by means of a uniform access algorithm.

\*OF = orderable function

Fig. 1-2 Software structure

The orderable functions (OF) address single functions (SF), to which a fixed task is assigned. The single functions cannot be directly addressed externally, however, and are the smallest units of the software structure.

# 1.3 Description of the MPST parallel bus

#### 1.3.1 Requirements

The MPST parallel bus is a multiprocessor bus system. The interests of the automation technology were in the forefront during its development. The structure of modern semiconductor components, especially that of microprocessors, was also taken into account.

A direct exchange of data between bus subscribers should be possible, whereby the amounts of data to be transmitted are composed of single bits, single words and data blocks (list transfers). Events with high priority require a fast alarm transmission.

The bus supervision is carried out via the central control unit (CCU). The CCU has as a subscriber the address 0 for the bus transfers. It also creates the control clock. CC.

A bus structure designed for a microprocessor is required in order to minimize the interface expenditure for the function unit to be connected to the bus. A free selection of the processor must be guaranteed with a view to the further development. The mixed operation of **8 bit processors** and **16 bit processors** is supported by the bus system.

Special weight was given to the possibility of a cheap serial production as well as on the field of application in an inclement environment. The control electronics is generally concentrated in a unit cabinet for controls for machining or processing devices. A bus length of 2 m is therefore sufficient.

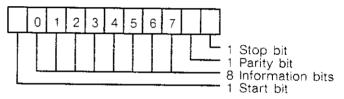

#### 1.3.2 Bus signals

The individual signals are described in the following.

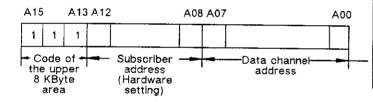

#### Address bus

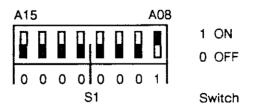

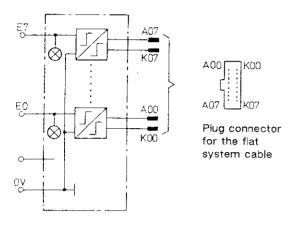

The 16 address lines are bi-directional bus lines. The address bit A00 is the address bit with the lowest value. The smallest bit, which can be addressed, is a byte. The driver outputs for the addresses have a high resistance, when they are not active, and the bus signals are logically one (2.3 V ... 5.25 V).

The subscriber is directly addressed by the address setting in the subscriber.

#### Data bus

The 16 data lines are bi-directional bus lines. The data bit D00 is the data bit with the lowest value. The driver outputs for the data have a high resistance, when they are not active, and the bus signals are logically one  $(2.3 \ V \dots 5.25 \ V)$ .

#### Control bus

The meaning of the signals is explained in the following.

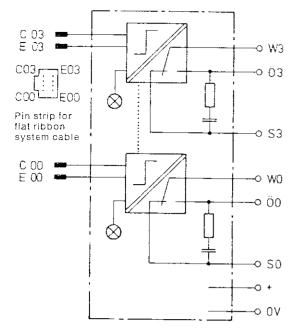

#### WO:

The signal WO (word transfer) codes the format of the data on the data bus (word/byte).

| A00 | wo | Address                                                                    |

|-----|----|----------------------------------------------------------------------------|

| 0   | 0  | even numbered byte address. Data in the lower byte (D00 to D07) are valid  |

| 1   | 0  | odd numbered byte address. The data in the                                 |

| 0   | 1  | higher byte (D08 to D15) are valid word address. The data in the lower and |

| 1   | 1  | higher bytes (D00 to D15) are valid<br>not defined                         |

#### $\overline{\mathsf{W}}$

Writes a word or byte under a given address. The entire address bus is valid.

#### R:

Reads a word or byte from the address given on the address bus. The entire address bus is valid.

| R           | W                | Meaning                                                                    |

|-------------|------------------|----------------------------------------------------------------------------|

| 0<br>0<br>1 | 0<br>1<br>0<br>1 | invalid<br>Read<br>Wrlte<br>only valid with ACK during interrupt operation |

#### $\overline{1/0}$ :

The signal  $\overline{I/O}$  (Input/Output memory area) codes the address area of 64 x 1024 addresses for the passive subscribers.

#### BB:

The signal  $\overline{BB}$  (Bus Busy) shows the bus occupation by an active subscriber.

#### RBB:

The signal  $\overline{\text{RBB}}$  (Resetting Bus Busy) displays that the bus is to be released immediately for the CCU (central control unit).

#### BOV:

The signal  $\overline{BOV}$  (Bus Operation Valid) codes a bus operation as valid.

#### RDY:

The signal RDY (Ready) displays to the sending subscriber, that the data were written or that they can be read. It is the acknowledgement signal for  $\overline{\text{BOV}}$ .

#### SPO

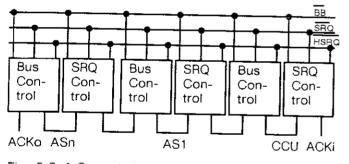

The signal  $\overline{SRQ}$  (Service Request) informs the CCU of one or more valid interrupts (collective interrupts). The identification of the subscriber sending the interrupt is carried out by means of the signals  $\overline{HSRQ}$  and ACK. The evaluation is carried out, when an interrupt vector is read by the CCU. A bus assignment is generally carried out afterwards by the CCU.

#### HSRQ:

The signal  $\overline{\text{HSRQ}}$  (Hold Status Service Request) displays to the subscribers, that an interrupt treatment is initiated. The interrupt status may no longer be changed.

#### ACK:

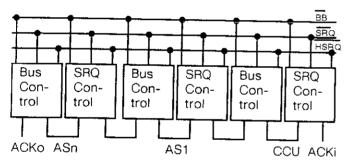

The signal ACK (Acknowledge) is output by the CCU for the identification of the subscriber giving the interrupt with the highest priority. For this, the signal is looped through all the subscribers and creates a priority chain, whereby it is only handed on to the next subscriber by the previous subscriber, if it has not had its own wish for an interrupt.

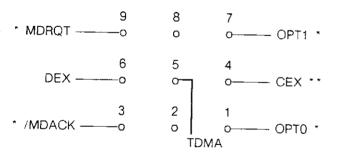

#### DMARO:

The signal DMARQ (DMA Request) applies for a direct memory access at the CCU.

#### **DMACK**

The signal DMACK (DMA Acknowledge) is created by the CCU. It is the acknowledgement signal of DMARQ.

#### SYNC:

The signal SYNC (Synchronisation Signal) starts subscribers maskable with the one-zero edge asynchronously to the bus operation.

#### RS:

The signal  $\overline{RS}$  (Reset) is used in order to bring all the subscribers to their starting status at the same time.

#### CC

The signal CC (Central Clock) is a central clock, which is formed on the CCU. Its frequency lies between 1 and 5 MHz, its pulse duty factor between 25% and 75%.

#### PFD:

The signal PFD (Power Failure Detect) codes a voltage failure.

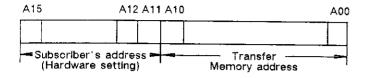

#### 1.3.3 Addressing the subscribers

The distinction between addressing passive and active subscribers is made by the signal  $\overline{1/0}$ .

#### Addressing active subscribers

Every active subscriber includes a transfer memory area to communicate in the ABB Procontic T300 sys-

tem. Active subscribers are addressed via A11 to A15  $(\overline{i/0}=1)$ . A00 to A10 addresses a memory position in the transfer memory area of the active subscriber (2 kbytes).

If a subscriber requires a larger transfer memory area (n times 2 kbytes), it can occupy several subscriber addresses.

#### Addressing passive subscribers

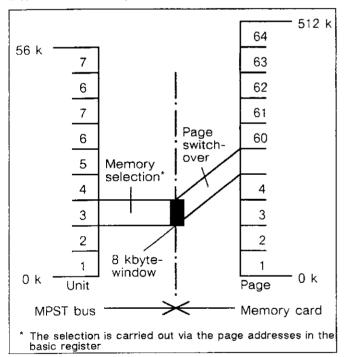

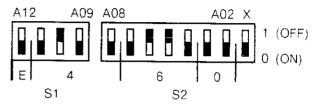

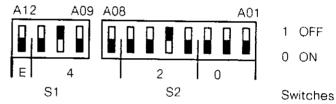

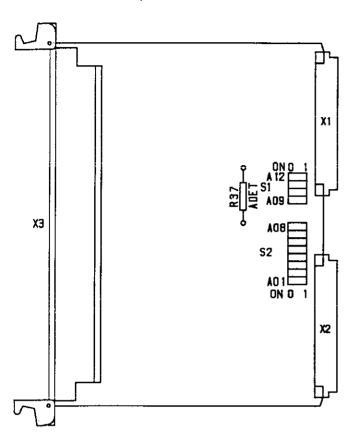

Passive subscribers are addressed by A00 to A15  $(\overline{I/O}=0)$ . The addresses smaller than 56 x 1024 are reserved for addressing the memory of the address area of 64 x 1024 addresses. The upper 8 x 1024 addresses are foreseen for data channels of passive subscribers; A08 to A12 therefore include the address of the respective subscriber.

The subscriber address of A05 to A12 or of A02 to A12 can be set for passive subscribers, which require a smaller address area for data channels.

#### 1.3.4 Bus operations

The following bus operations are foreseen for the MPST bus:

- Writing

- Reading

- DMA transfer

- Interrupt transfer

The exact sequences of the bus accesses are defined independently of the manufacturer in the MPST standard, DIN 66264 part 1.

#### 1.3.5 Exchange of data and access priority

Seen from the front of the subrack, the processor in the extreme right-hand slot has the highest priority as concerns the bus accesses. If a processor carries out a bus access, it cannot be interrupted. A processor can receive the bus access for several operations via the "Lock" mechanism.

The further to the left that a subscriber is slotted in the subrack, the less is its priority concerning bus accesses.

#### 1.4 Electrical characteristics

All levels are measured under load on the plug connector on the respective electronic card.

#### 1.4.1 Voltage supply

+5V DC (U<sub>B1</sub>), +15V DC (U<sub>B2</sub>) and -15V DC (U<sub>B3</sub>) are defined as voltage supplies. The tolerance values amount to +5%, -3%, referring to the nominal value.

#### 1.4.2 Signal levels (bus signals)

The electrical levels of the MPST bus signals are defined as follows:

|        |   | Voltage<br>range                         | Current limit value                                               |

|--------|---|------------------------------------------|-------------------------------------------------------------------|

| Input  | 1 | 0 V to 0.6 V<br>2.1 V to U <sub>B1</sub> | max. 0.5 mA<br>max. 20 μA<br>with GT<br>max. 60 μA<br>with T, OC  |

| Output | _ | 0 V to 0.5 V<br>2.3 V to U <sub>B1</sub> | min. 16 mA<br>min. 400 μA<br>with GT<br>min. 3.0 mA<br>with T, OC |

T = Tristate

OC = Open collector

GT = Realisation with push-pull or OC with a PULL-UP resistor on the module

#### 1. 4.3 Non-specified bus connections

The voltage for these connections may not exceed the limit of  $\pm$  42 V. A current of max. 500 mA is permitted.

#### 1.5 Mechanical structure

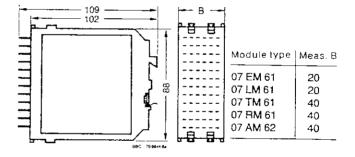

The subrack must correspond to DIN 41494, part 5. The size amounts to 19 inches, 6 height units. The assembly of the subrack is foreseen for switch cabinets with a depth of  $\geq$  400 mm. The printed boards have the format of 160 mm x 233.4 mm according to DIN 41494, part 2. Two 32-polar plug connectors in accordance with DIN 41612, part 2, in the constructive form C are used.

The corresponding socket connectors in accordance with DIN 41612, part 2, with the constructive form C are to be used as the mating component. The arrangement of the connectors is to be carried out according to DIN 41494, part 5, issue of September 1980, footnote 8.

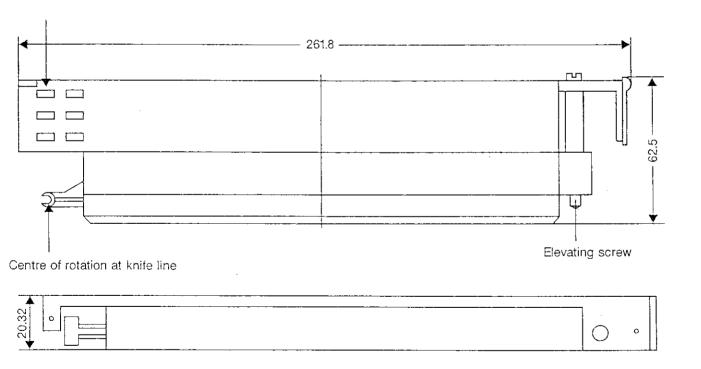

The increments, which can be used within the subrack, amount to  $84 \times 5.08$  mm. The distance between these slots amounts to 4 increments (20.32 mm) or whole number multiplications of 4. 21 possible slots for subracks result in this way, DIN 41494 A -6W - 164 - 84.

#### 1.6 Ambient conditions

| <ul> <li>Application categories and reliability data</li> </ul>                  | according to DIN 40 040                                      |

|----------------------------------------------------------------------------------|--------------------------------------------------------------|

| <ul> <li>Permitted ambient temperature: Operation</li> </ul>                     | 0 + 55 °C (Letter symbols KV)                                |

| <ul> <li>Transport and storage</li> </ul>                                        | - 25 + 85 °C (Letter symbols HP)                             |

| Relative humidity                                                                | ≤ 75 % annual average 95 % on 30 days/year (Letter symbol F) |

| <ul> <li>Permitted operating height</li> </ul>                                   | 0 2200 m above mean sea level (Letter symbol R)              |

| Degrees of protection                                                            | according to DIN 40 050, part 3                              |

| <ul> <li>Subracks, units</li> </ul>                                              | IP00                                                         |

| • Cabinets                                                                       | IP54                                                         |

| <ul> <li>Front of the operating panels</li> </ul>                                | IP65                                                         |

| Vibration test                                                                   | according to DIN VDE 0160/5.88                               |

| Radio interference level                                                         | according to DIN VDE 0871, limit value category B            |

| <ul> <li>Noise immunity to conducted, transient interference voltages</li> </ul> | according to IEC 801-4/draft 12.85                           |

| Communication interfaces                                                         | Test category 2 (0.5 kV)                                     |

| Supply connections                                                               | Test category 3 (2 kV)                                       |

| <ul> <li>Process in- and outputs 24 V DC</li> </ul>                              | Test category 3 (1 kV)                                       |

| <ul> <li>Process in– and outputs 220 V AC</li> </ul>                             | Test category 4 (2 kV)                                       |

Note: Deviations are listed separately within the description of the subracks/units.

2

# 2 Fans and Subracks

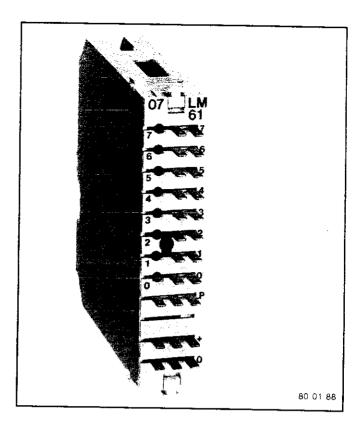

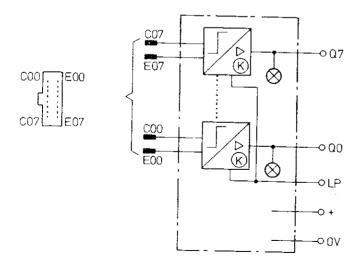

34 LU 31 R2: Fan for 220 V AC

35 GS 91 R1: Subrack with power supply unit 35 NE 90 R1, 220 V AC for  $\pm$  5 V DC/25 A,  $\pm$  15 V DC/1 A 35 GS 93 R1: Subrack with power supply unit 35 NE 93 R1, 24 V DC for  $\pm$  5 V DC/12 A,  $\pm$  15 V DC/2 A

### Contents, Chapter 2

| 2.1                                       | Fan 34 LU 31 R2                                                                               | 2.1- 1                               | 2.3                              | Subrack 35 GS 93 R1 with                                                     |                                      |

|-------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|------------------------------------------------------------------------------|--------------------------------------|

| 2.1.1<br>2.1.2<br>2.1.3                   | Technical data                                                                                | 2.1- 2<br>2.1- 2                     |                                  | a power supply unit 35 NE 93 R1 for 24 V DC voltage supply                   | 2.3- 1                               |

| 2.2                                       | Subrack 35 GS 91 R1 with<br>a power supply unit<br>35 NE 90 R1 for<br>220 V AC voltage supply | 2.2- 1                               | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4 | Technical data  Description  Mechanical structure  Dimensions of the subrack | 2.3- 2<br>2.3- 2<br>2.3- 2<br>2.3- 3 |

| 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5 | Technical data                                                                                | 2.2- 2<br>2.2- 2<br>2.2- 2<br>2.2- 3 | 2.3.5                            | Supply voltage and earth connection of the subrack 35 GS 93 R1               | 2.3- 4                               |

| 2.2.3                                     | the subrack                                                                                   | 2.2- 4                               |                                  | 35 NE 93 R1                                                                  | 2.3- 5                               |

#### 2.1.1 Technical data

| Inputs with 220 V AC, 50 Hz | 35 W         |  |

|-----------------------------|--------------|--|

| Inputs with 220 V AC, 60 Hz | 45 W         |  |

| Weight                      | 2.5 kg       |  |

| Order number                | GJV3071301R2 |  |

#### 2.1.2 Description

A fan must be installed under each basic subrack (see the planning manual, volume 5). The fan 34 LU 31 is designed as a tangential fan with a filter mat and an airflow monitor.

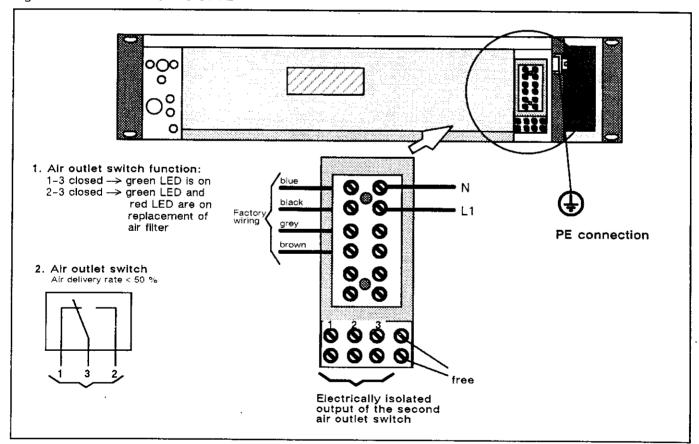

#### 2.1.3 Connecting the fan 34 LU 31

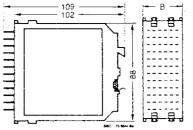

Height of the fan 34 LU 31: 88.7 mm (2 height modules)

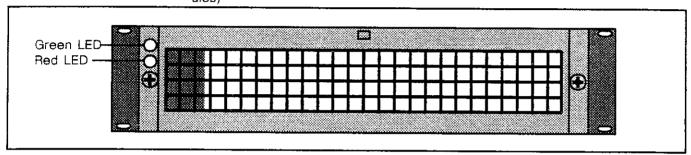

Fig. 2.1-1: Front view 34 LU 31 R2

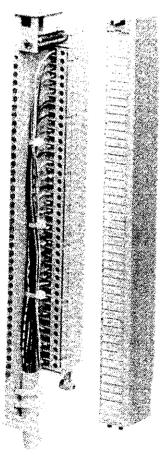

Fig. 2.1-2: Rear view 34 LU 31 R2

Without an ON/OFF switch; green indicator lamp for correct functioning. If the air delivery rate in the fan sinks below 50%, the green lamp stays alight and the red lamp lights up as well, replacement of the air filter. The operating status of the fan can be output on the

control via a floating contact (250 V AC and/or DC,  $5 \, A$ ).

# 2.2 Subrack 35 GS 91 R1 with a power supply unit 35 NE 90 R1 for 220 V AC voltage supply

#### 2.2.1 Technical data

#### Subrack 35 GS 91 R1:

Component slots

Earthing arrangement

Humidity rating

Weight (with power supply unit)

Order number

16

Faston 6.3 mm on the subrack

F according to DIN 40 040 without moisture condensa-

tion

8.94 kg

GJR5136400R1

#### Power supply unit 35 NE 90 R1:

Supply voltage UP Current input

Output UB1

Output UB2 Output UB3

External fuses Connection Weight

Order number

220 V AC + 10 % / - 15 %

max. 2 A

+ 5 V DC, 25 A + 15 V DC, 1A - 15 V DC, 1 A

3.15 A time-lag

6.3 mm rear Faston terminal

3.5 kg

GJV3180801R1

#### Accessories:

Fan 34 LU 31 R2

GJV3071301R2

#### 2.2.2 Description

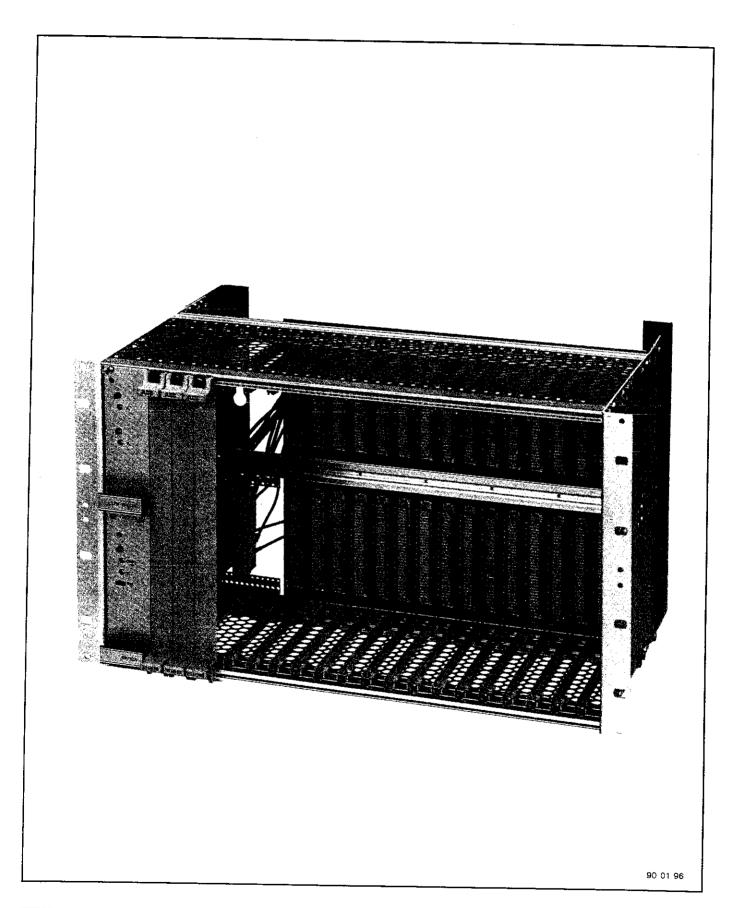

The subrack 35 GS 91 with a bus printed board and a power supply unit is foreseen for connecting ABB Procontic T300 units.

The bus printed board is attached to the subrack, so that the right-hand edges are aligned.

A power supply unit 35 NE 90 is assembled on the left-hand side and requires 5 slots. The power supply unit works for low power dissipation using a primary-switch mode.

If the voltage of the power supply unit fails for longer than 20 ms on the input side, a corresponding signal  $\overline{PFD}$  (Power Failure Detect) is generated for the power failure. The output voltage is buffered for at least a further 5 ms, until it falls below the tolerance limit. The monitoring circuit for the output voltage then generates

a reset signal  $(\overline{RS})$ . The controller can rescue information concerning the current status in a buffery memory in the meantime.

A fan **must** be installed under each basic subrack (see the planning manual, volume 5). The fan 34 LU 31 to be integrated is designed as a tangential fan (see chapter 2.1) with a filter mat and an air flow monitoring.

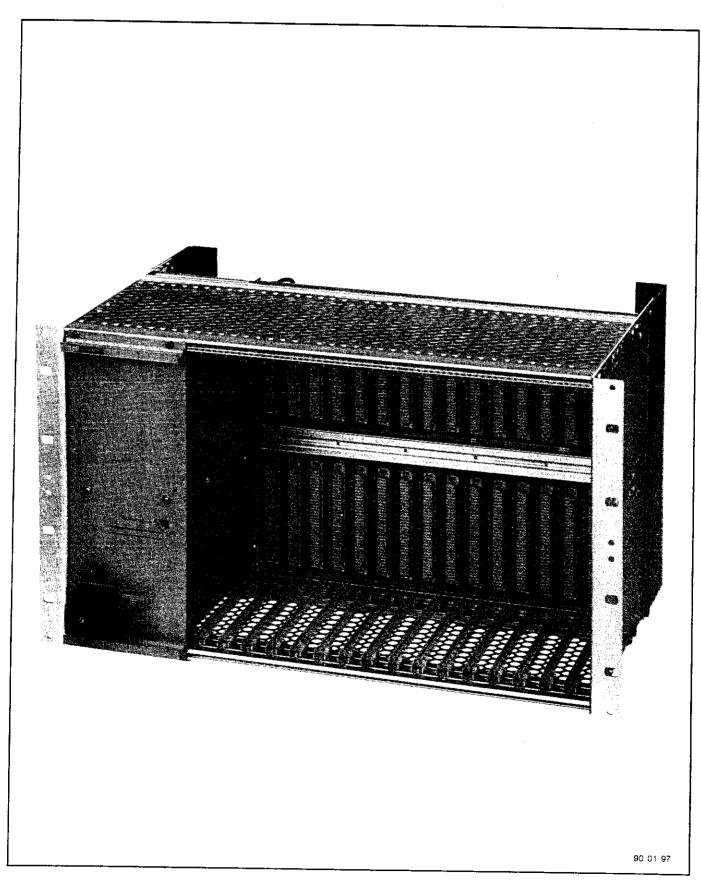

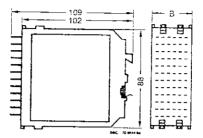

#### 2.2.3 Mechanical structure

The subrack is built for the connection of printed boards in the double-size Eurocard format 233.4 mm x 160 mm x 20.32 mm. It can be installed into a 19" frame in accordance with DIN 41494. The side walls and the longitudinal sections are made from zinc-coated plates, and the guide mats are made from plastic.

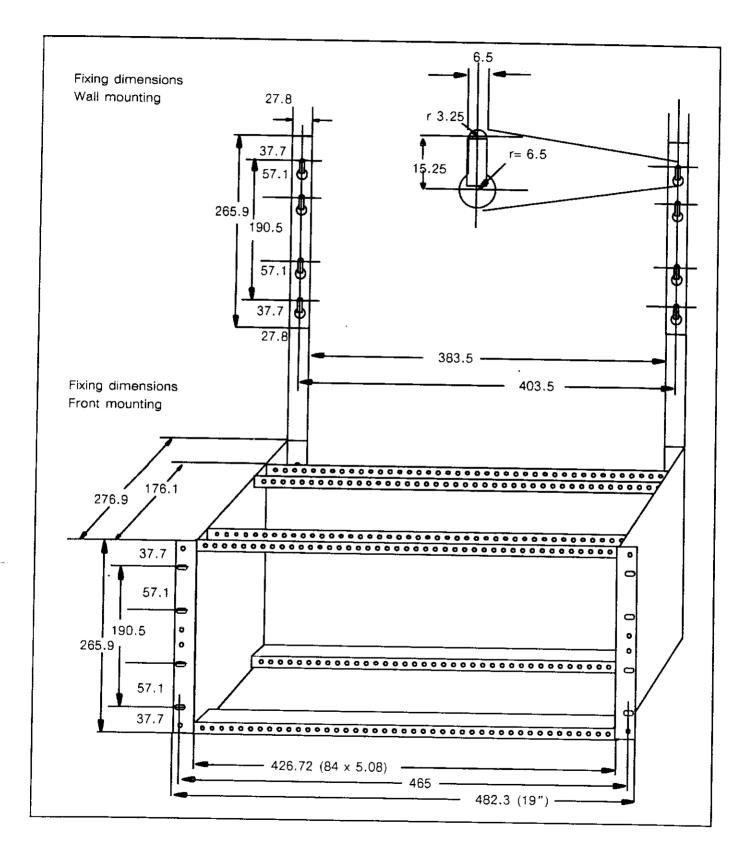

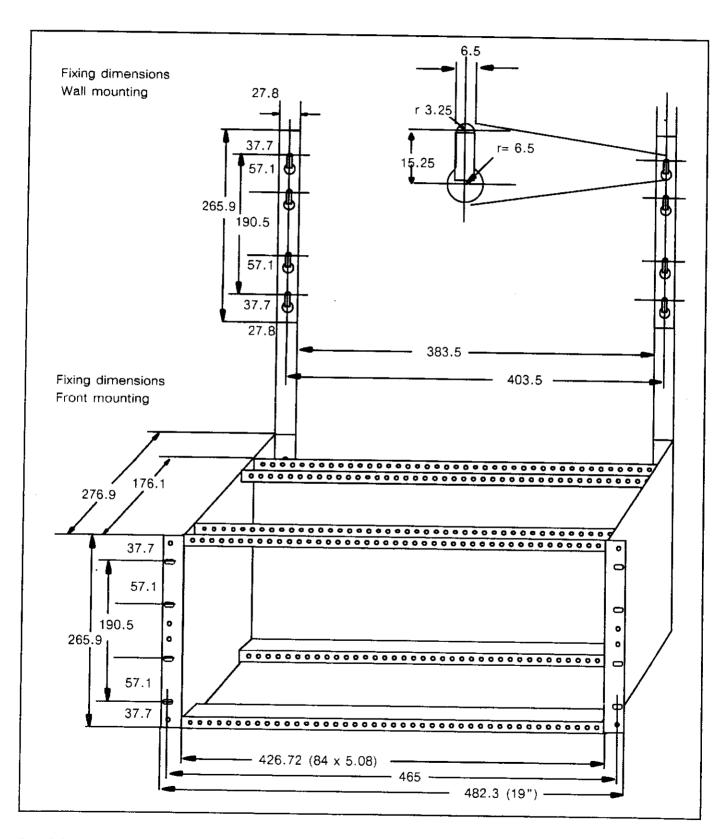

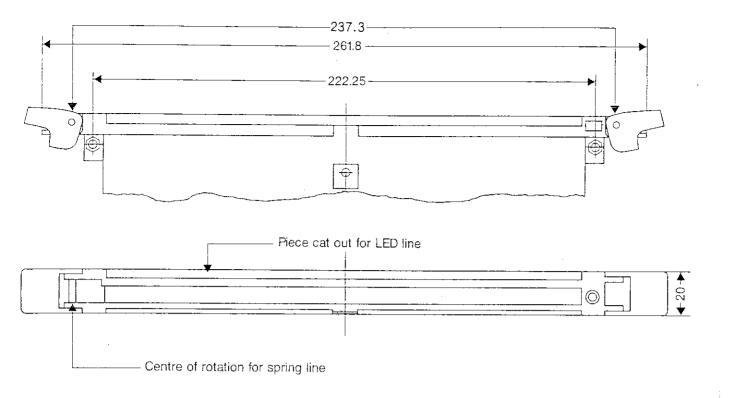

#### 2.2.4 Dimensions of the subrack

The dimensions of the subrack are:

Height: 265.9 mm (< 6 height units, 1 height unit = 44.45 mm)

Width: 426.72 mm (84 pitches, 1 pitch = 5.08 mm)

Width with clamps: 482.3 mm Depth: 276.9 mm

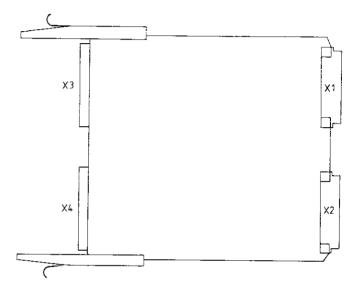

Fig. 2.2-1 Frame of the subrack

# 2.2.5 0 V DC and earth terminal of the subrack

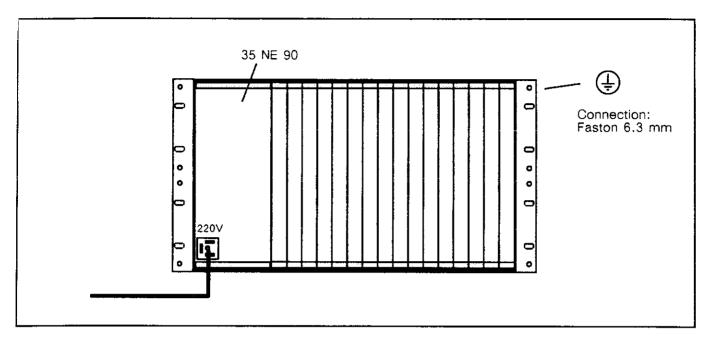

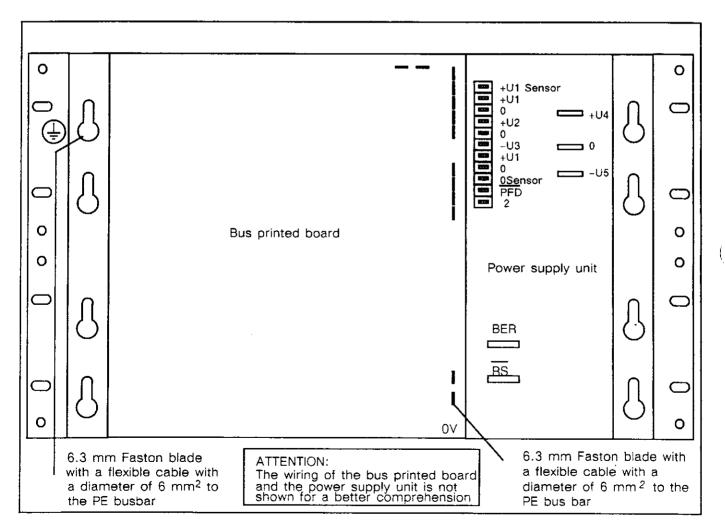

Fig. 2.2-2: 35 GS 91 with a power supply unit 35 NE 90

Fig. 2.2-3; Rear view of the subrack 35 GS 91 R1

# 2.3 Subrack 35 GS 93 R1 with a power supply unit 35 NE 93 R1 for 24 V DC voltage supply

#### Subrack 35 GS 91 R1:

Component slots Earthing arrangement

Humidity rating

Weight (with power supply unit)

Order number

16

Faston 6.3 mm on the subrack

F according to DIN 40 040 without moisture condensa-

7.0 kg

GJR514400R1

#### Power supply unit 35 NE 93 R1:

Supply voltage UP Current input

Output UB1 Output UB2 Output UB3

External fuses Connection Weight

Order number

24 V DC ± 30 % max. 6.6 A

+ 5 V DC, 12 A + 15 V DC, 2 A - 15 V DC, 2 A

10 A time-lag

6.3 mm rear faston terminal

2.0 kg

GJV3072601R1

#### Accessories:

Fan 34 LU 31 R2

GJV3071301R2

#### 2.3.2 Description

The subrack 35 GS 93 with a bus printed board and a power supply unit is foreseen for connecting ABB Procontic T300 units.

The bus printed board is attached to the subrack, so that the right-hand edges are aligned.

A power supply unit 35 NE 93 is assembled on the left-hand side and requires 2 slots. The power supply unit 35 NE 93 can supply a partially equipped subrack depending on the current input of the installed units. A second power supply 35 NG 93 can be installed, if necessary. The in- and output voltages of the power supply unit are monitored.

If the voltage of the power supply unit fails for longer than 20 ms on the input side, a corresponding signal PFD (Power Failure Detect) is generated for the power failure. The output voltage is buffered for at least a further 1.5 ms until it sinks below the tolerance level. The monitoring circuit for the output voltage then generates a reset signal (RS). The control can rescue information concerning the current status in a buffer memory in the meantime.

A fan must be installed under each basic subrack (see the planning manual, volume 5). The fan 34 LU 31 to be integrated is designed as a tangential fan (see chapter 2.1) with a filter mat and an air flow monitoring.

#### 2.2.3 Mechanical structure

The subrack is built for the connection of printed boards in the double-size Eurocard format 233.4 mm x 160 mm x 20.32 mm. It can be installed into a 19" frame in accordance with DIN 41494. The side walls and the longitudinal sections are made from zinc-coated plates, and the guide mats are made from plastic.

#### 2.3.4 Dimensions of the subrack

The dimensions of the subrack are:

Height:

265.9 mm (< 6 height units, 1 height unit = 44.45 mm)

Width:

426.72 mm (84 pitches, 1 pitch = 5.08 mm)

Width with clamps: 482.3 mm Depth:

276.9 mm

Fig. 2.3-1 Frame of the subrack

# 2.3.5 Supply voltage and earth connection of the subrack 35 GS 93 R1

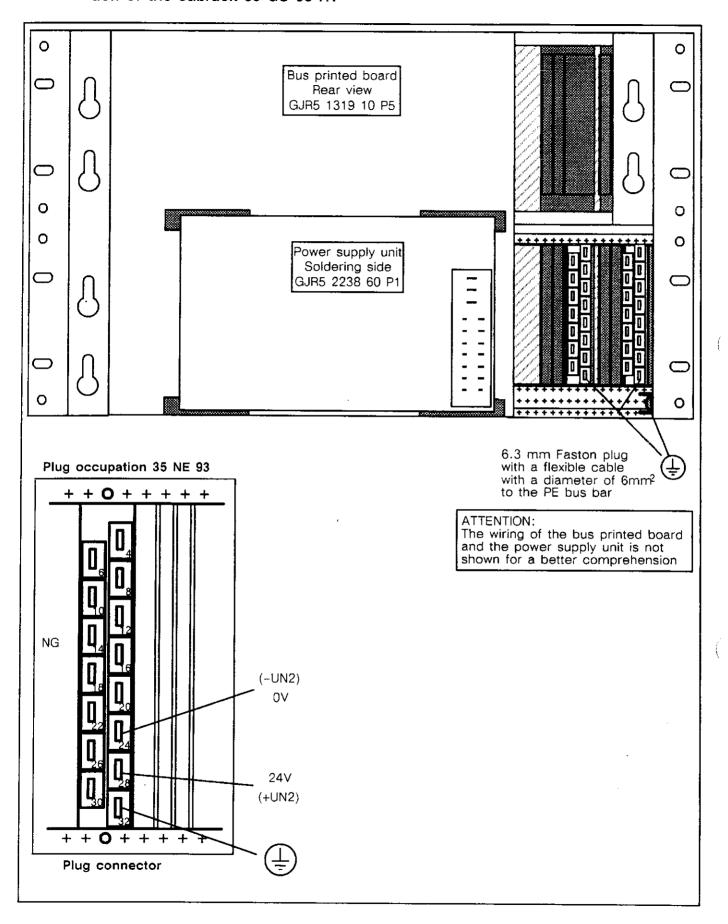

Bild 2.3-2 Rear view of the subrack 35 GS 93 R1

# 2.3.6 Adjustment regulations when using two power supply units 35 NE 93 R1

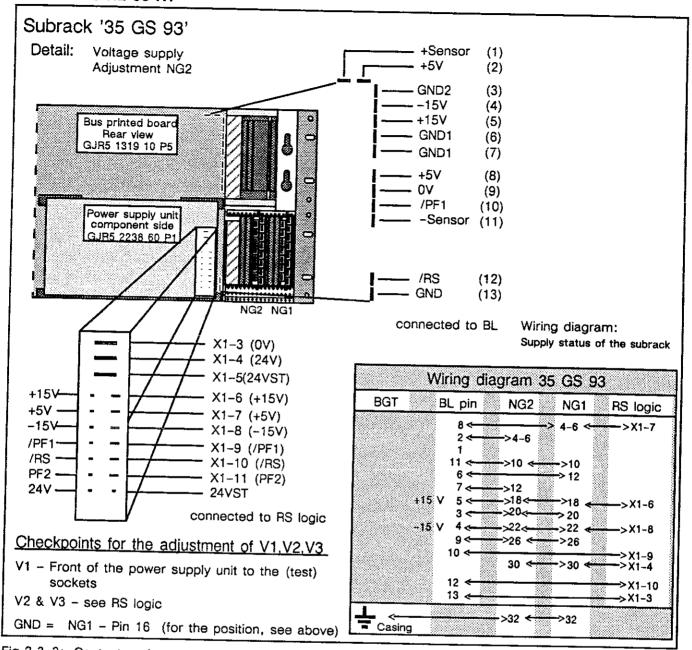

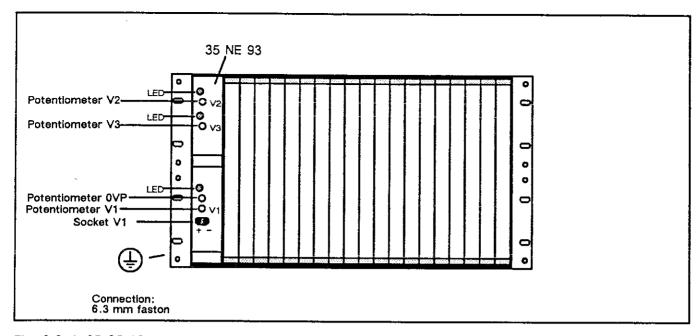

Fig.2.3-3: Contact assignment/wiring diagram 35 GS 93

- Measure and note the voltage value 'V<sub>1</sub>','V<sub>2</sub>','V<sub>3</sub>'

of the power supply unit already located in the subrack but without a load. NG1 is the reference unit for

the adjustment of NG2.

- Swap the power supply units. The unit NG2 must occupy the left-hand slot of the subrack during the adjustment. (Do not plug in NG11)

- 3. Adjust the voltage " $V_1$ " of the secondary unit to the determined value ( $\Delta V_1 = V_1 \pm 0.1\%$ ). The adjustment is carried out with the potentiometer ( $V_1$ ), which can be reached through the front panel.

- 4. The adjustment for V2 and V3 done in the factory is sufficient. In exceptional cases the adjustment is to be done as follows:

Adjust the voltage " $V_2$ " of the secondary unit to the determined value ( $\Delta V_2 = V_2 \pm 0.1\%$ ). The adjustment is carried out with the potentiometer ( $V_2$ ), which can be reached through the front panel.

Adjust the voltage " $V_3$ " of the secondary unit to the determined value ( $\Delta V_3 = V_3 \pm 0.1\%$ ). The adjustment is carried out with the potentiometer ( $V_3$ ), which can be reached through the front panel.

- 5. Return the reference unit (NG1) to its previous position.

- Remove the blanking plates and plug in the adjusted power supply unit (NG2) next to the reference unit.

Fig. 2.3-4: 35 GS 93 with the power supply unit 35 NE 93

# 3 Power supply units

35 NE 93 R1: Power supply unit 24 V DC for + 5 V DC/12 A, ± 15 V DC/2 A

### Contents, Chapter 3

| 3.1   | Power supply unit            |        |

|-------|------------------------------|--------|

|       | 35 NE 93 R1 for              |        |

|       | 24 V DC voltage supply       | 3.1- 1 |

| 3,1.1 | Technical data               | 3.1- 2 |

| 3.1.2 | Description                  | 3.1- 2 |

| 3.1.3 | Mechanical structure         | 3.1- 2 |

| 3.1.4 | Adjustment regulations when  |        |

|       | using two power supply units |        |

|       | 35 NE 93 R1                  | 3 1- 2 |

# 3.1 Power supply unit 35 NE 93 R1 for 24 V DC voltage supply

#### **Technical Data** 3.1.1

| Supply voltage UP | 24 V DC ± 30 %              |

|-------------------|-----------------------------|

| Current input     | max. 6.6 A                  |

| Output UB1        | + 5 V DC, 12 A              |

| Output UB2        | + 15 V DC, 2 A              |

| Output UB3        | - 15 V DC, 2 A              |

| External fuses    | 10 A time-lag               |

| Connection        | 6.3 mm rear Faston terminal |

| Dimension         | 2 pitches                   |

| Weight            | 2.0 kg                      |

| Order number      | GJV3072601R1                |

#### 3.1.2 Description

A power supply unit 35 NE 93 is assembled on the left-hand side of the subrack 35 GS 93 R1 and requires 2 slots. The power supply unit 35 NE 93 can supply a partially equipped subrack depending on the current input of the installed units. A second mains unit 35 NG 93 can be installed, if necessary. The in- and output voltages of the power supply unit are monitored.

If the voltage of the power supply unit fails for longer than 20 ms on the input side, a corresponding signal PFD (Power Failure Detect) is generated for the power failure. The output voltage is buffered for at least a further 1.5 ms until it sinks below the tolerance level. The monitoring circuit for the output voltage then gen-

erates a reset signal (RS). The control can rescue information concerning the current status in a buffer memory in the meantime.

#### 3.1.3 Mechanical structure

card of double-size Eurocard format 160 x 233.4 mm, 2 pitches.

#### 3.1.4 Adjustment regulations when using two power supply units 35 NE 93 R1

See section 2.3.6.

## 4 Bus coupler units

35 EK 90 R1: Bus coupler unit for the basic subrack. 35 EK 91 R1: Bus coupler unit for the extension subrack.

35 SK 96 R1: Connecting cable betweeen the bus coupling units.

Example of a bus coupling.

### Contents, Chapter 4

| 4.1                                                         | Bus coupler unit<br>35 EK 90 R1 for                                                                                                                                                                                                                                        | 4.2.6<br>4.2.7          | Settings 4 Soldering bridges for                     |                |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------|----------------|

|                                                             | the basic subrack 4.1-1                                                                                                                                                                                                                                                    |                         | cable screens 4                                      | .2- 3          |

| 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.1.7 | Technical data       4.1- 2         Description       4.1- 2         Function       4.1- 2         Example of a bus coupling       4.1- 2         Mechanical structure       4.1- 3         Settings       4.1- 3         Soldering bridges for cable screens       4.1- 3 | 4.3.1<br>4.3.2<br>4.3.3 | Connecting cable 35 SK 96 R1 for bus coupler units   | .3- 2<br>.3- 2 |

| 4.2                                                         | Bus coupler unit 35 EK 91 R1 for the extension subrack 4.2- 1                                                                                                                                                                                                              | 4.4                     | Example of a bus coupling with the bus coupler units |                |

| 4.2.1                                                       | Technical data 4.2- 2                                                                                                                                                                                                                                                      |                         | 35 EK 90, 35 EK 91                                   |                |

| 4.2.2                                                       | Description 4.2- 2                                                                                                                                                                                                                                                         |                         | and the connecting cable                             | _              |

| 4.2.3                                                       | Function 4.2- 2                                                                                                                                                                                                                                                            |                         | 35 SK 96 4.                                          |                |

| 4.2.4                                                       | Example of a bus coupling 4.2-2                                                                                                                                                                                                                                            | 4.4.1                   | Description 4.                                       |                |

| 4.2.5                                                       | Mechanical structure 4.2-3                                                                                                                                                                                                                                                 | 4.4.2                   | Example 4.                                           | .4- 2          |

|                                                             |                                                                                                                                                                                                                                                                            |                         |                                                      |                |

# 4.1 Bus coupler unit 35 EK 90 R1 for the basic subrack

#### 4.1.1 Technical data

Positive supply voltage UB1

Supply current IB1 to UB1 without a bus terminator Supply current IB1 to UB1 with a bus terminator

Ambient temperature Storage temperature Humidity rating Mechanical stress

Dimensions Weight

Additional consignment

Order number

$+5 V \pm 5 \%$

typically 1.0 A, max. 1.4 A typically 1.4 A, max. 1.8 A

0 °C ... +55 °C -25 °C ... +75 °C

F

in accordance with VDE 160 when installed

1 pitch

1.0 kg

2 sub-printed boards with matching resistors, 2 dummy plugs for the front plugs, which are not occupied

GJR5143100R1

Accessories

Bus coupler unit 35 EK 91 R1 for the extension subracks

GJR5143200R1

Connecting cable 35 SK 96 R1 for the bus coupler units.

GJR5143700R1

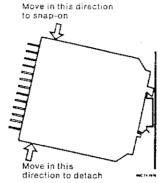

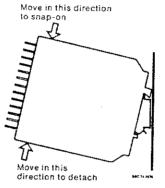

#### 4.1.2 Description

A basic subrack (master) is connected to a maximum of three extension subracks (slaves) by means of the bus coupler units 35 EK 90, 35 EK 91 and the connecting cable 35 SK 96. The subracks to be connected to each other are placed on top of each other. The lowest subrack is connected to a bus coupler unit 35 EK 90 (so that the installation of the above—mentioned fan is possible below) and is thus the basic subrack. The extension subracks are placed above this and equipped with one bus coupler unit 35 EK 91 each.

#### Note:

The maximum distance between the lower edges of the two subracks amounts to 240 mm caused by the length of the cable 35 SK 96.

The bus coupler unit 35 EK 90 is designed, so that active and passive subscribers can be included in the basic subrack. In the extension subrack only passive subscribers without an interrupt can be included.

The lines of the system cable 35 SK 96 and the connecting lines between the front plugs of the bus coupler units form a bus, the repeater bus. The repeater bus, as an open collector bus, must be terminated on the first and last bus coupler unit with resistors. Sub printed boards, which can be plugged in, are used together with matching resistors. Two sub-printed boards are included as an addition to the delivery scope for the unit 35 EK 90.

The bus operations 'read' and 'write' are possible using the repeater bus.

#### ATTENTION:

In order to protect the bus coupler units from electro-

static contact, their non-occupied front plugs (X3 or X4) must be provided with dummy plugs. Two of these dummy plugs are also included in the delivery scope of the unit 35 EK 90.

#### 4.1.3 Function

The unit 35 EK 90 extends the writing/reading cycle to 1.8  $\mu s$  in order to achieve a safe method of transfer. The exchange of data in the I/O area of the MPST bus is only affected here.

The unit behaves like a passive user with a  $\overline{BOV}/RDY$  delay of 1.8  $\mu s$ , which occupies all the I/O addresses.

The repeater bus transfers the MPST bus signals A, D,  $\overline{I/O}$ ,  $\overline{R}$ ,  $\overline{W}$ , WO,  $\overline{BOV}$ , RDY.

Control signals for the bus drivers in the extension subracks (GTAS and GTDS for slaves) or in the basic subrack (GTAM and GTDM for masters) are also formed as gate signals for addresse and data.

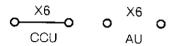

The signals PFD, CC, RS (multiprocessor-based control bus signals) as well as ADET and OUTINH (optional signals) can be addressed directly with the corresponding bus contacts using the jumper zone X6.

#### 4.1.4 Example of a bus coupling

See section 4.4.

#### 4.1.5 Mechanical structure

Unit in the double-size Eurocard format 160 x 233.4 mm, 1 pitch

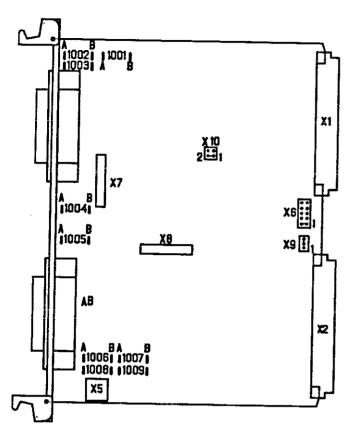

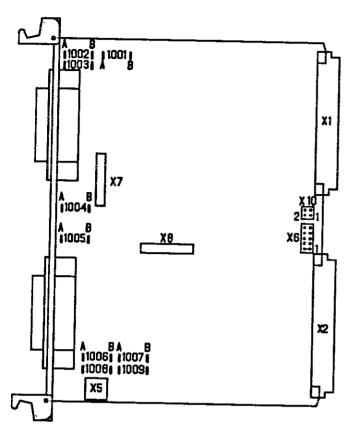

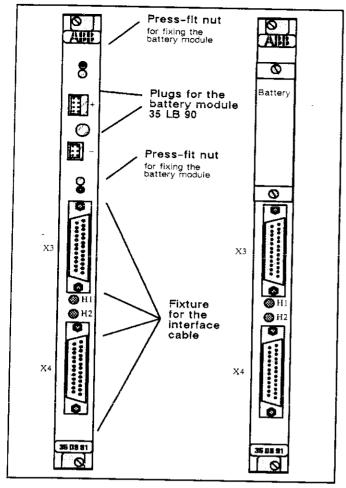

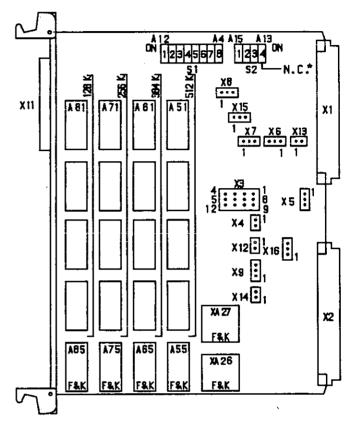

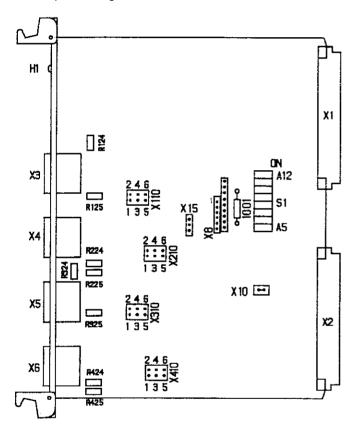

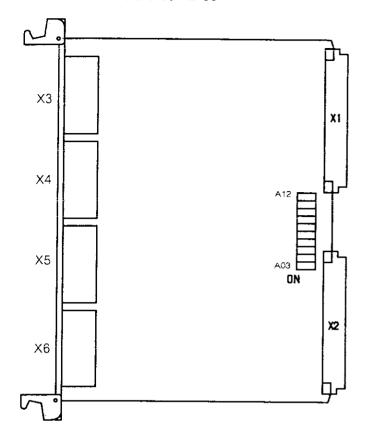

Fig. 4.1-1 Component side (top view)

The drawn jumpers correspond to the factory setting; see also section 4.1.6, Settings.

| X 1, X 2  | Plug connectors with MPST bus signals according to DIN 66264                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| X 3, X 4  | Plug connectors (50-polar) for the re-<br>peater bus RB, system cable 35 SK 96<br>connection, provided with dummy<br>plugs if not occupied |

| X 5       | Optional 0 V terminal                                                                                                                      |

| X 6       | Disconnectable connection for PFD, RS, CC,                                                                                                 |

|           | ADET, OUTINH to the repeater bus                                                                                                           |

| X 7, X 8  | Plugs for the matching resistors of the repeater bus                                                                                       |

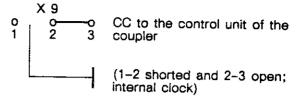

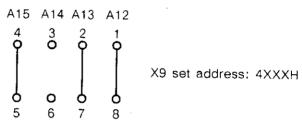

| X 9       | CC/internal clock switchover                                                                                                               |

| X10       | RDY control                                                                                                                                |

| 1001 1009 | wiring as required                                                                                                                         |

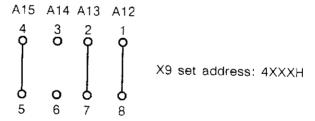

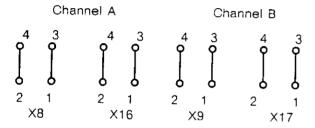

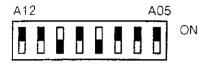

#### 4.1.6 Settings

(Standard setting of the unit is drawn each time)

Clock signal setting X9:

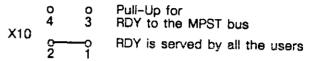

#### READY signal setting X10:

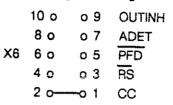

#### Various signal settings X6:

| 10 o |      | 09              | OUTINH |

|------|------|-----------------|--------|

| X6   | 8 0  | o 7             | ADET   |

|      | 6 o  | o 5             | PFD    |

|      | 4 o  | 03              | RS     |

|      | 2 o- | <del></del> 0 1 | CC     |

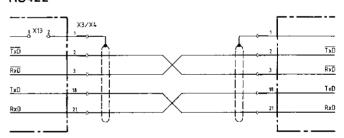

# 4.1.7 Soldering bridges for cable screens

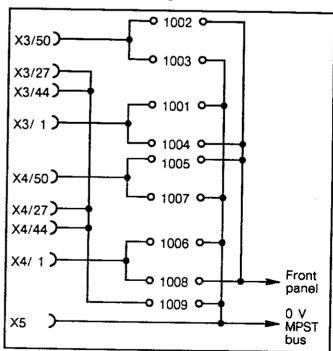

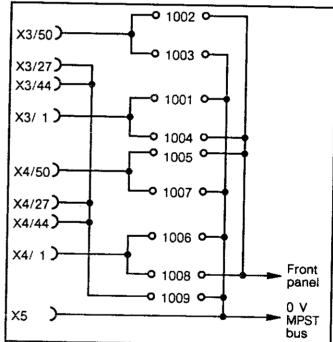

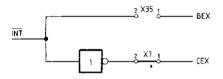

The soldering bridges for the 0 V or the front panel connection of the cable screens of the system cable 35 SK 96 are shown in Fig. 4.1-2.

Fig. 4.1-2 Soldering bridges

The assignment of the plug connectors X3 and X4 is as follows:

| X*/1  | Screen, cable 1 |

|-------|-----------------|

| X*/27 | 0 V, cable 1    |

| X*/44 | 0 V, cable 2    |

| X*/50 | Screen, cable 2 |

2

# 4.2 Bus coupler unit 35 EK 91 R1 for the extension subrack

#### 4.2.1 Technical data

Positive Supply voltage UB1

Supply current to UB1 without a bus terminator Supply current IB1 to UB1 with a bus terminator

Ambient temperature Storage temperature Humidity rating Mechanical stress

Dimensions Weight

Order number

+5 V +/-5 %

typically 0.8 A, max. 1.1 A typically 1.2 A, max. 1.5 A

0 °C ... +55 °C -25 °C ... +75 °C

F

in accordance with VDE 160 when installed

1 pitch 1.0 kg

GJR5143200R1

#### Accessories

Bus coupler unit 35 EK 90 R1 for the extension subracks

GJR5143100R1

Connecting cable 35 SK 96 R1 for the bus coupler units

GJR5143700R1

#### 4.2.2 Description

A basic subrack (master) is connected to a maximum of three extension subracks (slaves) by means of the bus coupler units 35 EK 90, 35 EK 91 and the connecting cable 35 SK 96. The subracks to be connected to each other are placed on top of each other. The lowest subrack is connected to a bus coupler unit 35 EK 90 (so that the installation of the above–mentioned fan is possible below) and is thus the basic subrack. The extension subracks are placed above this and equipped with one bus coupler unit 35 EK 91 each.

#### Note:

The maximum distance between the lower edges of the two subracks amounts to 240 mm caused by the length of the cable 35 SK 96.

The bus coupler unit 35 EK 91 is designed, so that only passive subscribers without an interrupt transfer can be included in the extension subrack.

The lines of the system cable 35 SK 96 and the connecting lines between the front plugs of the bus coupler units form a bus, the repeater bus. The repeater bus, as an open collector bus, must be terminated on the first and last bus coupler unit with resistors. Sub-printed boards, which can be plugged in, are used together with matching resistors. Two sub-printed boards are included as an addition to the delivery scope for the unit 35 EK 90.

The bus operations "reading" and "writing" are possible using the repeater bus.

#### ATTENTION:

In order to protect the bus coupler units from electrostatic contact, their non-occupied front plugs (X3 or X4) must be provided with dummy plugs. Two of these dummy plugs are also included in the delivery scope of the unit 35 EK 90.

#### 4.2.3 Function

The unit 35 EK 90 extends the writing/reading cycle to 1.8  $\mu s$  in order to achieve a safe method of transfer. The exchange of data in the I/O area of the MPST bus is only affected here.

The unit behaves like a passive subscriber with a  $\overline{BOV}/$  RDY delay of 1.8  $\mu s$ , which occupies all the I/O addresses.

The repeater bus transfers the MPST bus signals A, D,  $\overline{I/O}$ ,  $\overline{R}$ ,  $\overline{W}$ , WO,  $\overline{BOV}$ , RDY.

Control signals for the bus drivers in the extension subracks (GTAS and GTDS (for slaves) or GTAM and GTDM (for masters) as gate signals for addresses and data).

The signals PFD, CC, RS (MPST bus signals) as well as ADET and OUTINH (optional signals) can be addressed directly with the corresponding bus contacts using the jumper zone X6.

#### 4.2.4 Example of a bus coupling

See section 4.4.

## 4.2.5 Mechanical structure

Unit in the double-size Eurocard format 160 x 233.4 mm, 1 pitch.

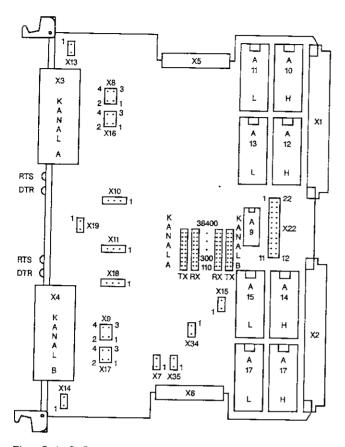

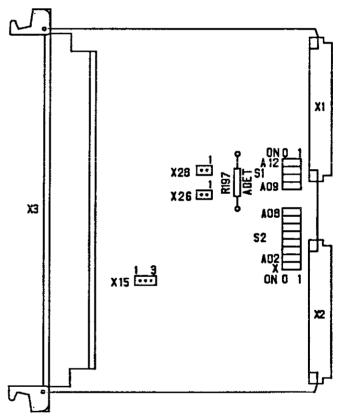

Fig. 4.2-1 Component side (top view)

The drawn jumpers correspond to the factory setting, see also section 4.2.6, Settings.

| X 1, X 2                | Plug connectors with MPST bus signals according to DIN 66264                                                                               |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| X 3, X 4                | Plug connectors (50-polar) for the re-<br>peater bus RB, system cable 35 SC 96<br>connection, provided with dummy<br>plugs if not occupied |

| X 5                     | Optional 0 V terminal                                                                                                                      |

| X 6                     | Disconnectable connection for PFD, RS, CC, ADET, OUTINH to the repeater bus                                                                |

| X 7, X 8                | Plugs for the matching resistors of the repeater bus                                                                                       |

| X 9<br>X10<br>1001 1009 | CC/internal clock switchover<br>RDY control<br>Wiring as required                                                                          |

#### 4.2.6 Settings

(Standard setting of the unit is drawn each time)

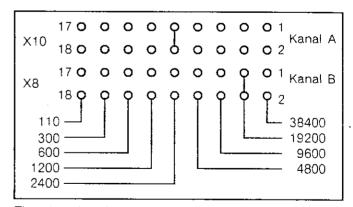

READY signal setting X10:

| V10 | 0<br>4 | 3 | Pull-Up for<br>RDY to the MPST bus |

|-----|--------|---|------------------------------------|

| X10 | 2      | 0 | RDY is served by all the users     |

Various signal settings X6:

# 4.2.7 Soldering bridges for cable screens

The soldering bridges for the 0 V or the front panel connection of the cable screens of the system cable 35 SK 96 are shown in Fig. 4.2-2.

Fig. 4.2-2 Soldering bridges

The assignment of the plug connectors X3 and X4 is as follows:

| X*/1  | Sreen, cable 1  |

|-------|-----------------|

| X*/27 | 0 V, cable 1    |

| X*/44 | 0 V, cable 2    |

| X*/50 | Screen, cable 2 |

2

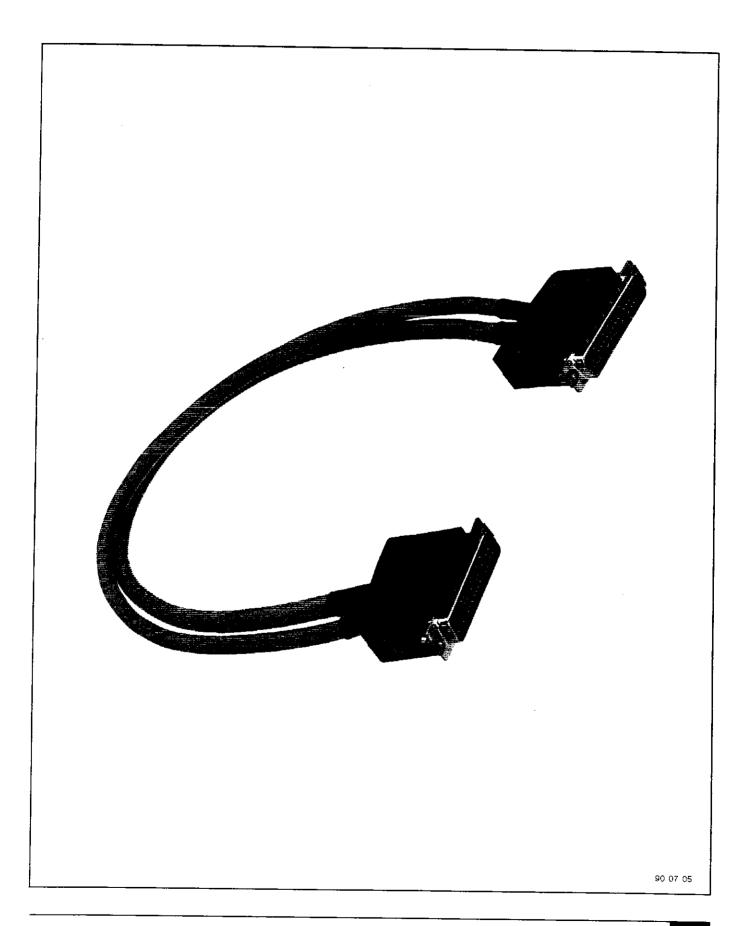

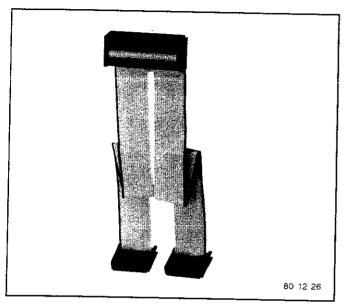

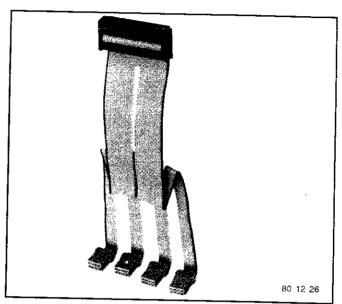

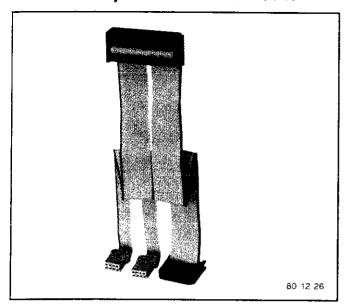

# 4.3 Connecting cable 35 SK 96 R1 for the bus coupler units

#### 4.3.1 Technical data

Cable with Weight SUB D plug, 50-polar

0.1 kg

Order number

GJR5143700R1

#### Accessories

Bus coupler unit 35 EK 90 R1 for the basic subrack Bus coupler unit 35 EK 91 R1 for the extension subrack

GJR5143100R1

GJR5143200R1

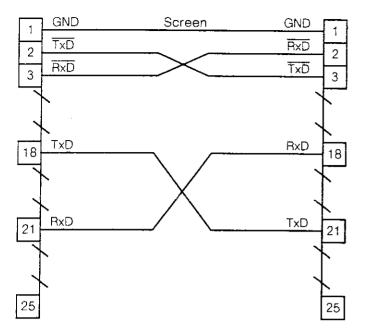

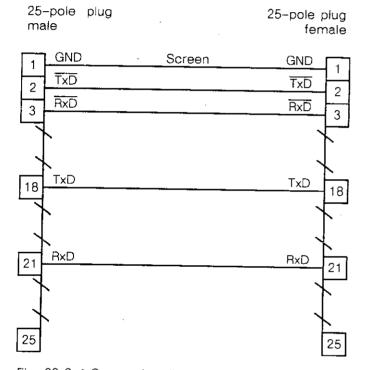

#### 4.3.2 Description

A basic subrack (master) is connected to a maximum of three extension subracks (slaves) by means of the bus coupler units 35 EK 90, 35 EK 91 and the connecting cable 35 SK 96. The subracks to be connected to each other are placed on top of each other. The lowest subrack is connected to a bus coupler unit 35 EK 90 (so that the installation of the above–mentioned fan is possible below) and is thus the basic subrack. The extension subracks are placed above this and equipped with one bus coupler unit 35 EK 91 each.

The lines of the system cable 35 SK 96 and the connecting lines between the front plugs of the bus coupler units form a bus, the repeater bus. The repeater bus, as an open collector bus, must be terminated on the first and last bus coupler unit with resistors. Sub printed boards, which can be plugged in, are used together with matching resistors.

The bus operations 'read' and 'write' are possible using the repeater bus.

The repeater bus transfers the ABB Procontic T300 control signals A, D,  $\overline{I/O}$ ,  $\overline{R}$ ,  $\overline{W}$ , WO,  $\overline{BOV}$ , RDY.

Control signals for the bus drivers in the extension subracks (GTAS and GTDS (for slaves) or GTAM and GTDM (for masters) as gate signals for addresses and data).

#### Note:

The maximum distance between the lower edges of the two subracks amounts to 240 mm caused by the length of the cable 35 SK 96.

# 4.3.3 Soldering bridges for cable screens

The soldering bridges for the 0 V or the front panel connection of the cable screens of the system cable 35 SK 96 are described in sections 4.1 and 4.2.

# 4.4 Example of a bus coupling with the bus coupler units 35 EK 90, 35 EK 91 and the connecting cable 35 SK 96

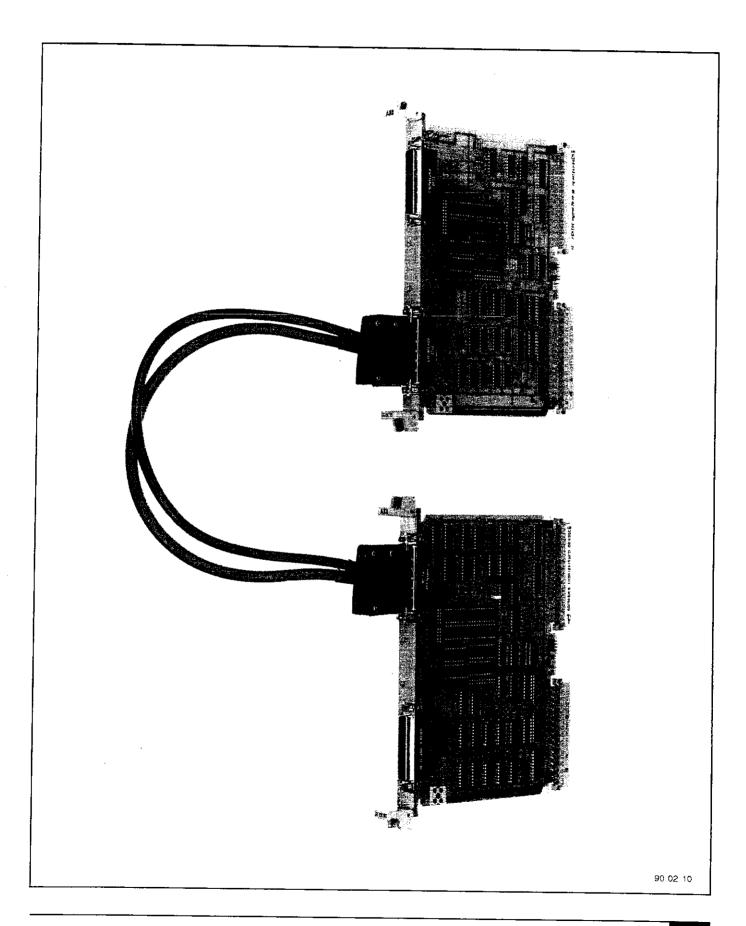

#### 4.4.1 Description

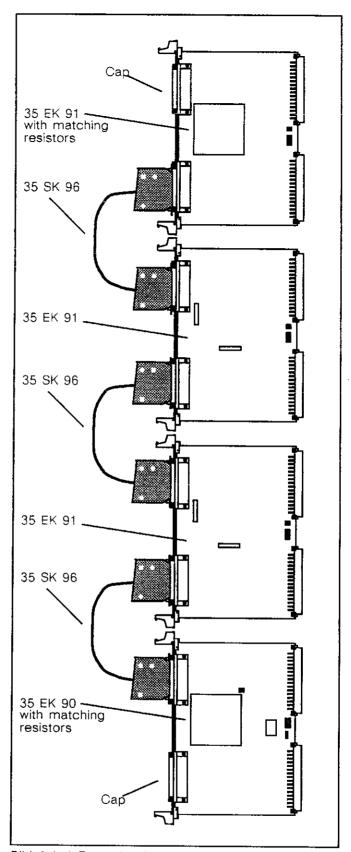

A basic subrack (master) is connected to a maximum of three extension subracks (slaves) by means of the bus coupler units 35 EK 90, 35 EK 91 and the connecting cable 35 SK 96. The subracks to be connected to each other are placed on top of each other. The lowest subrack is connected to a bus coupler unit 35 EK 90 (so that the installation of the above–mentioned fan is possible below) and is thus the basic subrack. The extension subracks are placed above this and equipped with one bus coupler unit 35 EK 91 each.

The bus coupler unit 35 EK 90 is designed, so that active and passive subscribers can be included in the basic subrack. Only passive subscribers without an interrupt transfer can be included in the extension subracks with the bus coupler units 35 EK 90.

The lines of the system cable 35 SK 96 and the connecting lines between the front plugs of the bus coupler units form a bus, the repeater bus. The repeater bus, as an open collector bus, must be terminated on the first and last bus coupler unit with resistors. Sub-printed boards, which can be plugged in, are used together with matching resistors. Two sub-printed boards are included as an addition to the delivery scope for the unit 35 EK 90.

The bus operations 'read' and 'write' are possible using the repeater bus.

#### ATTENTION:

In order to protect the bus coupler units from electrostatic contact, their non-occupied front plugs (X3 or X4) must be provided with dummy plugs. Two of these dummy plugs are also included in the delivery scope of the unit 35 EK 90.

#### 4.4.2 Example

Example with three extension subracks for one basic subrack.

Bild 4.1-1 Example of a coupler structure

#### Note:

The maximum distance between the lower edges of two subracks amounts to 240 mm caused by the length of the cable 35 SK 96.

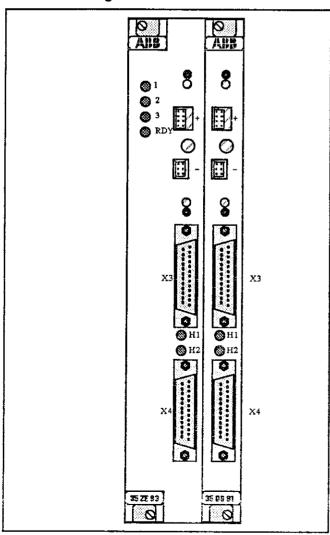

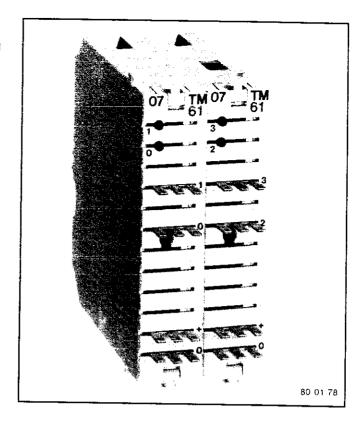

#### **Processor cards** 5

Processor card 35 PS 93 R11, equipped with 8086. Processor card 35 PS 93 R21, equipped with 8086 and 8087.

Processor card 35 PS 93 R31, equipped with 8086.

Processor card 35 PS 93 R41, equipped with 8086 and 8087.

| 5.1      | Processor card               |                     | 5.2                     | Prozessorkarte               |                 |

|----------|------------------------------|---------------------|-------------------------|------------------------------|-----------------|

| 0.1      |                              | E 4 4               | J.2                     |                              | <b>50</b> 4     |

| - 4 4    | 35 ZP 93 R11, R21            |                     |                         | 35 ZP 93 R31, R41            | 5.2- 1          |

| 5.1.1    | Technical data               | 5.1- 2              | 5.2.1                   | Technical data               | 5.2- 2          |

| 5.1.2    | Description                  | 5.1- 2              | 5.2.2                   | Description                  | 5.2- 2          |

| 5.1.3    | Mechanical structure         | 5.1- 2              | 5.2.3                   | Mechanical structure         | 5.2- 2          |

| 5.1.4    | Plug assignment              | 5.1- 3              | 5.2.4                   | Plug assignment              | 5.2- 3          |

| 5.1.4.1  | MPST bus interface,          |                     | 5.2.4.1                 | MPST bus interface,          |                 |

|          | plugs X1, X2                 | 5.1- 3              |                         | plugs X1, X2                 | 5.2- 3          |

| 5.1.4.2  | Wire wrap zone X3            | 5.1- 4              | 5.2.4.2                 | Wire wrap zone X3            | 5.2- 4          |

| 5.1.4.3  | System bus                   | 5.1- 5              | 5.2.4.3                 | System bus                   | 5.2- 5          |

| 5.1.5    | Function and structure       | 5.1- 6              | 5.2.5                   | Function and structure,      | 5.2- 6          |

| 5.1.5.1  | CPU and NDP                  | 5.1- 6              | 5.2.5.1                 | CPU and NDP                  | 5.2- 6          |

| 5.1.5.2  | Wait State Logik             | 5.1- 6              | 5.2.5.2                 | Wait State Logik             | 5.2- 6          |

| 5.1.5.3  | DMA                          | 5.1- 6              | 5.2.5.3                 | DMA                          | 5.2- 6          |

| 5.1.5.4  | Memory                       | 5.1- 6              | 5.2.5.4                 | Memory                       | 5.2- 6          |

| 5.1.5.5  | Transfer memory              | 5.1- 6              | 5.2.5.5                 | Transfer memory              | 5.2- 6          |

| 5.1.5.6  | MPST bus transfer            | 5.1-17              | 5.2.5.6<br>5.2.5.7      | MPST bus transfer            | 5.2- 7          |

| 5.1.5.7  | I/O units                    | 5.1-8               | 5.2.5.7                 | I/O units                    | 5.2- 8          |

| 5.1.5.8  | Ready Time Out               | 5.1- 9              | 5.2.5.8                 | Ready Time Out               | 5.2- 9          |

| 5.1.5.9  | Frequency divider            | 5.1- 9              | 5.2.5.10                | Frequency divider            | 5.2- 9          |

| 5.1.5.10 | Memory overview              | 5.1-10              | 5.2.5.10<br>5.2.6       | Memory overview              | 5.2-10          |

| 5.1.5.11 | NMI - non-masked Interrupt   | 5.1-10              | 5.2.6.1                 | Timing                       | 5.2-10          |

| 5.1.6    | Timing                       | 5.1-10              | 5.2.6.1                 | Internal access times        | 5.2-10          |

| 5.1.6.1  | Internal access times        | 5.1-10              | 5.2.6.3                 | MPST bus access times        | 5.2–10          |

| 5.1.6.2  | MPST bus access times        | 5.1-11              | 5.2.6.3<br><b>5.2.7</b> | Transfer memory access times | 5.2-10          |

| 5.1.6.3  | Transfer memory access times | 5.1-11              | 5.2.7.1                 | Settings                     | 5.2-11          |

| 5.1.7    | Settings                     | 5.1-11              | 5.2.7.1                 |                              | 5.2-11          |

| 5.1.7.1  | CCU/AS                       | 5.1-11              | 5.2.7.3                 | Transfer memory              | 5.2–11          |

| 5.1.7.2  | Transfer memory              | 5.1-11              | 5.2.7.5                 | dress                        | y au-<br>5.2-11 |

| 5.1.7.3  | Subscriber number and        |                     | 5.2.7.4                 | RAM/EPROM                    | 5.2-11          |

|          | transfer memory address      | 5.1-11              | 5.2.7.5                 | Wait state                   | 5.2-11          |

| 5.1.7.4  | RAM/EPROM                    | 5.1-12              | 5.2.7.6                 | MPST bus clock               | 5.2-12          |

| 5,1.7.5  | Wait state                   | 5.1-12              | 5.2.8                   | Model differences between    | 5.4-14          |

| 5.1.7.6  | MPST bus clock               | 5.1-12              | J                       | 35 ZP 93 R31, R41 and        |                 |

|          |                              | - · · · <del></del> |                         | 35 ZP 93 R11, R12            | 5.2-12          |

|          |                              |                     |                         |                              | J. Z - 1 Z      |

#### 5.1.1 Technical data

Processor Co-Processor Supply voltage

Current input

Power loss

Frequency cycle

Ambient temperature Storage temperature

Humidity rating

Mechanical stress when installed

Dimensions

Weight

Order number 35 ZP 93 with 8086 Order number 35 ZP 93 with 8086/8087 8086

8087 (only for rubric 21)

5 V DC ± 5 %

$2.8 A \pm 20 \%$

15 W ± 30 %

5 MHz

0 °C ... +55 °C

-25 °C ... +75 °C

F

VDE 0160

1 pitch

0.4 kg

GJR5133200R11 GJR5133200R21

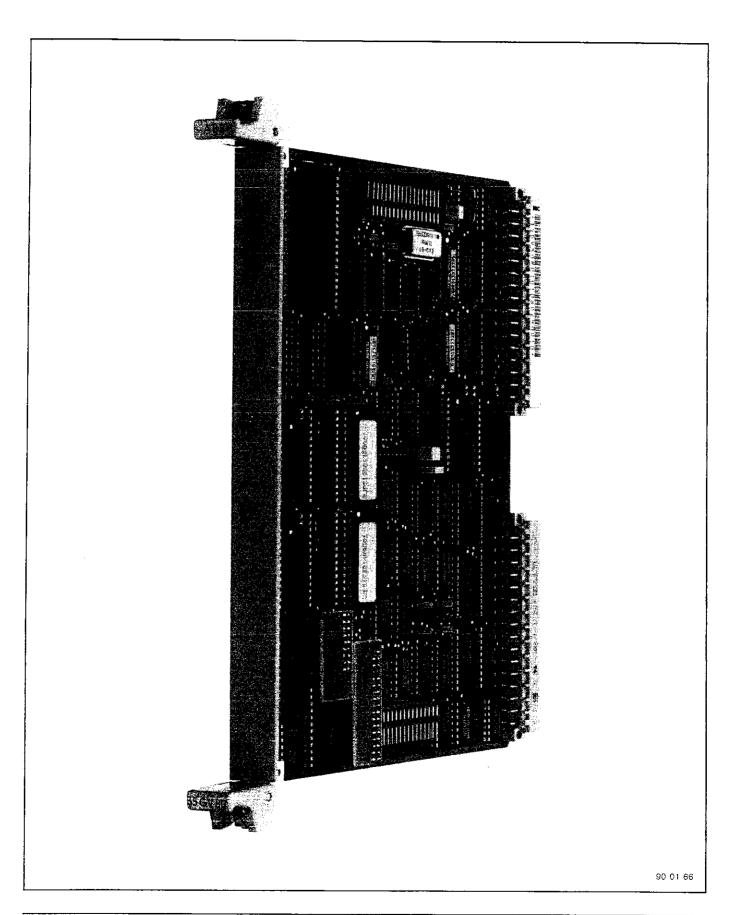

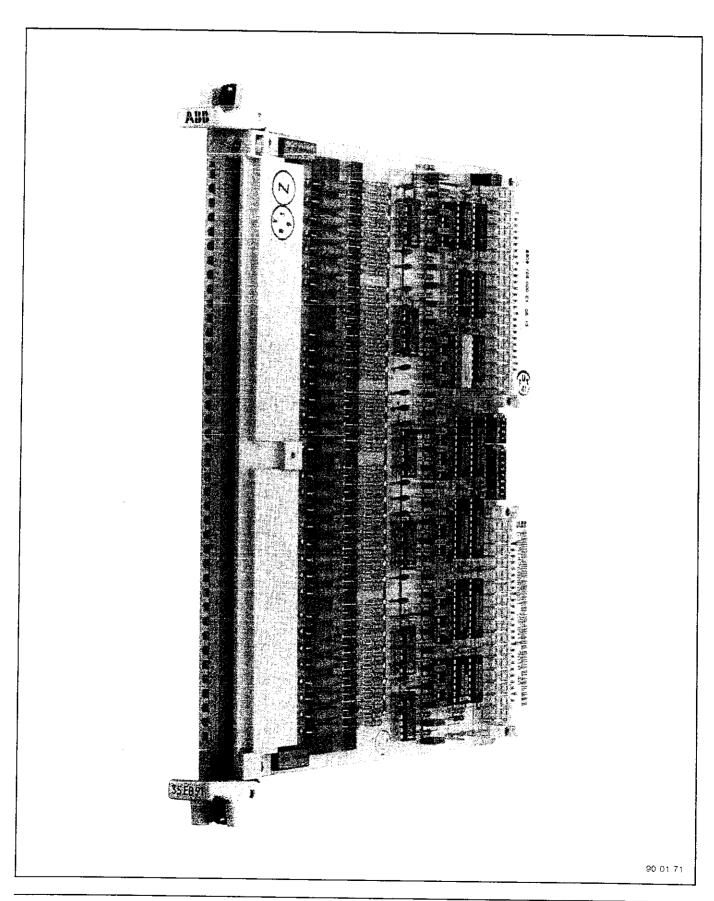

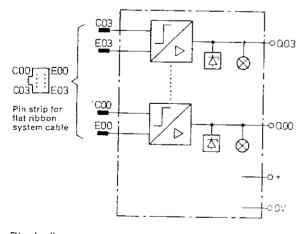

#### 5.1.2 Description

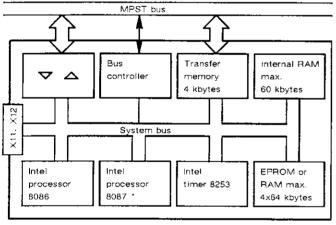

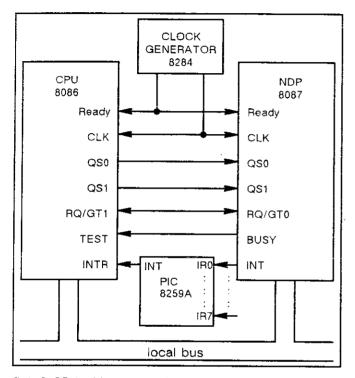

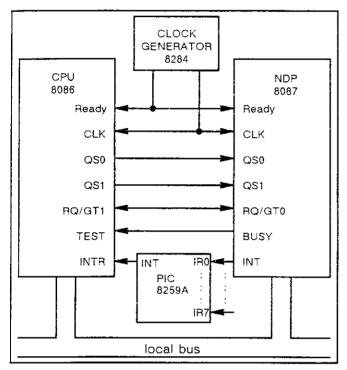

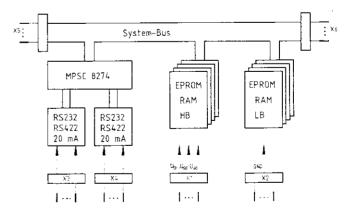

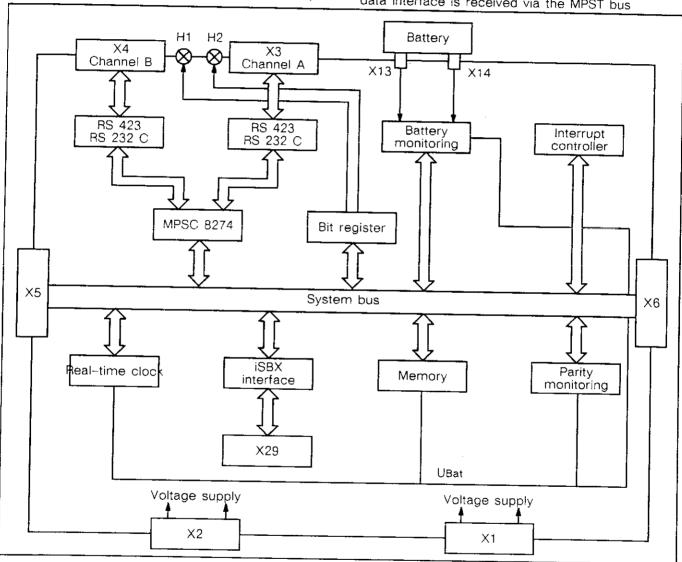

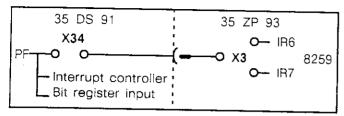

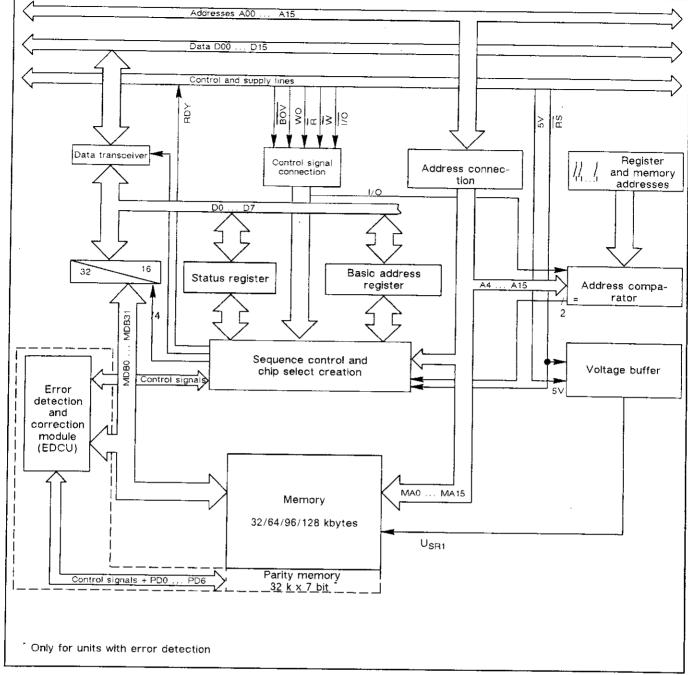

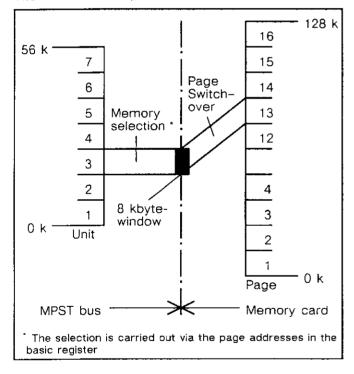

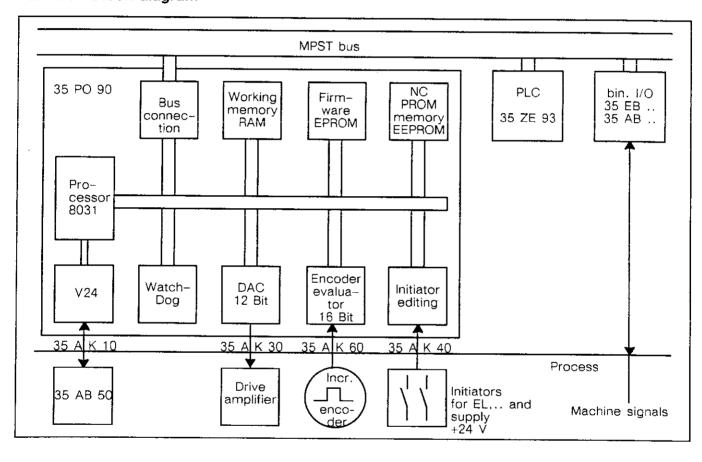

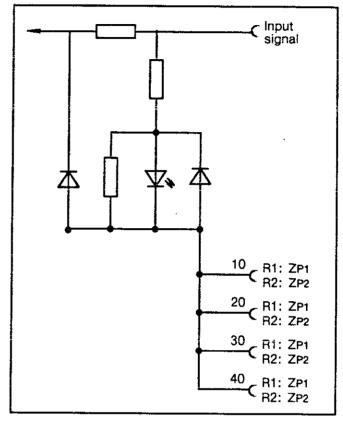

The central processor card 35 ZP 93 can be used as the central unit (CU) or as an active subscriber (AS) of the multiprocessor control system ABB Procontic T300. A coprocessor 8087 can be used as an option for a fast calculation of geometric data. The exchange of data between the 8086 and the 8087 is carried out via the local bus, between the 35 ZP 93 and the 35 DS 90 via the system bus and to other active or passive subscribers via the MPST bus. The card can process interrupts from the MPST bus and the system bus. 3 timers and several I/O ports are also freely available.

optional equipment

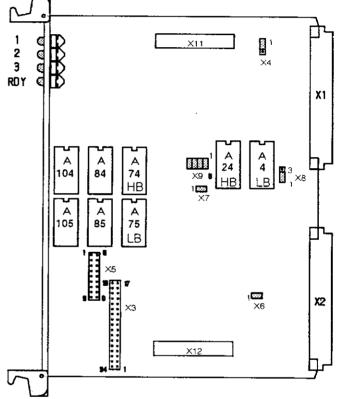

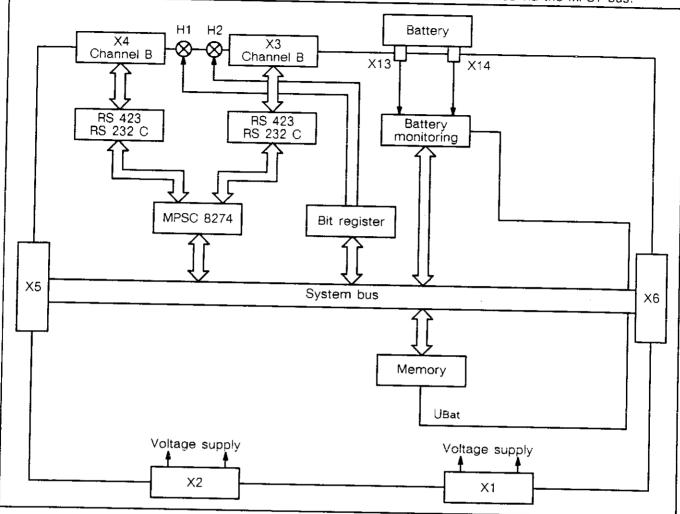

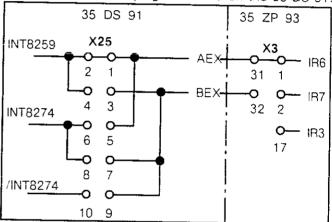

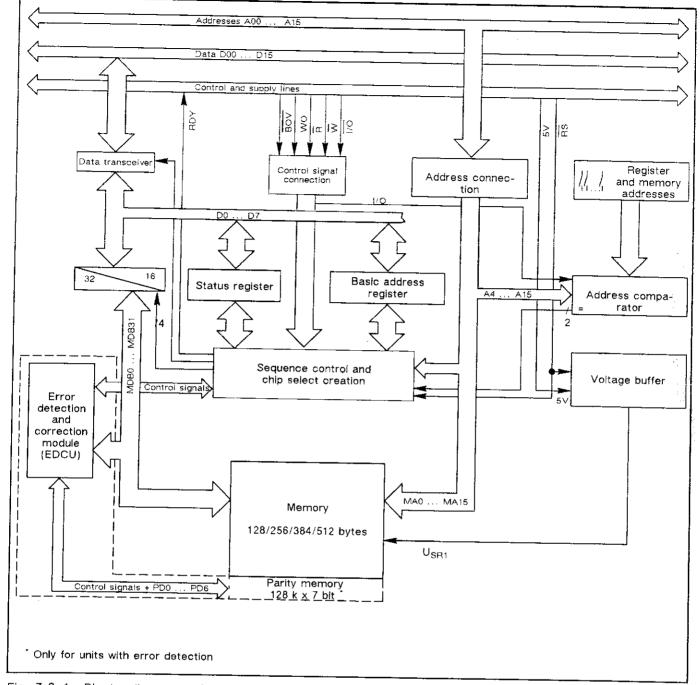

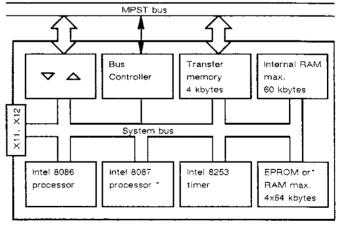

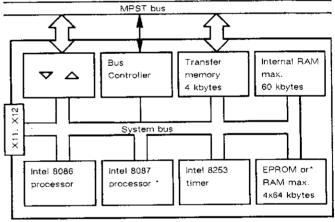

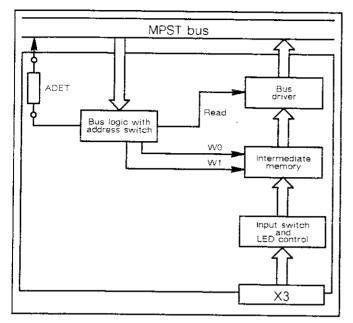

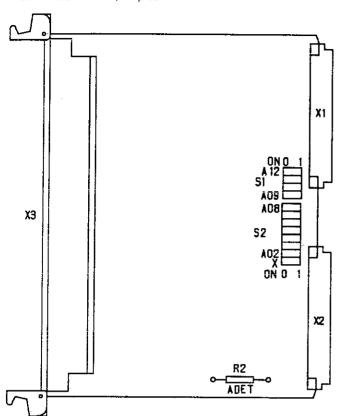

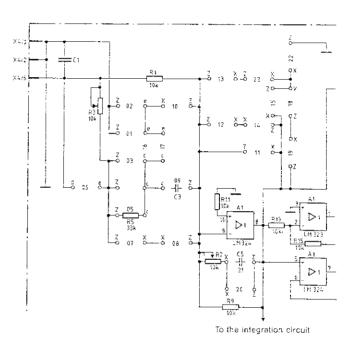

Fig. 5.1-1 Block diagram

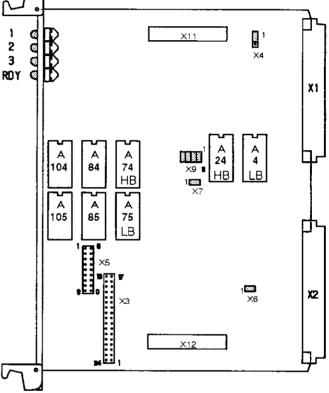

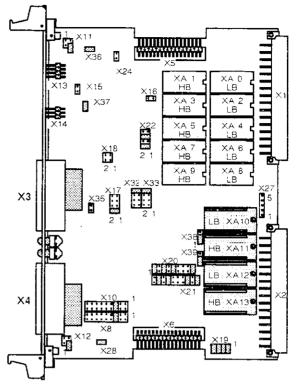

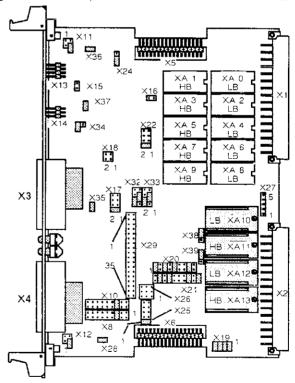

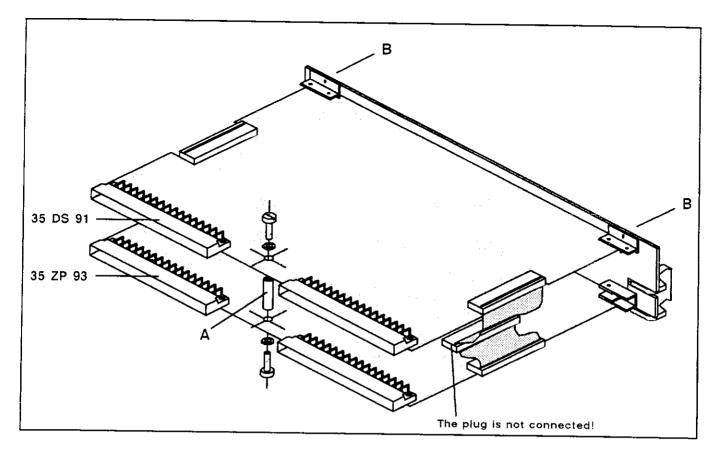

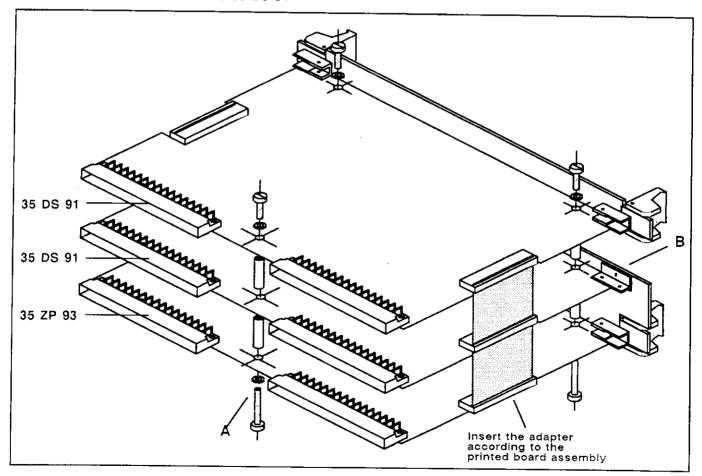

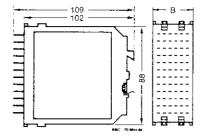

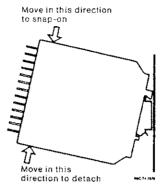

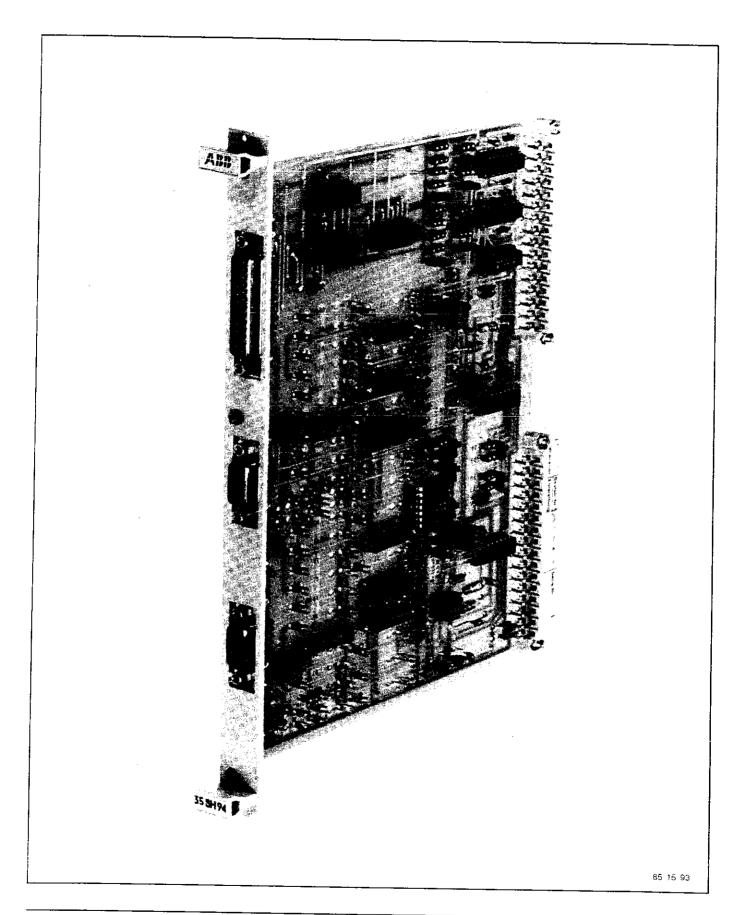

#### 5.1.3 Mechanical structure

Unit in the double-size Eurocard format 160 x 233.4 mm, 1 pitch.

A maximum of two data interfaces 35 DS 90 or 35 DS 91 can be connected to the 35 ZP 93.

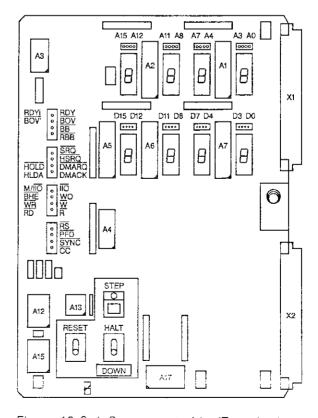

The drawn jumpers correspond to the factory setting; see also section 5.1.7, Settings.

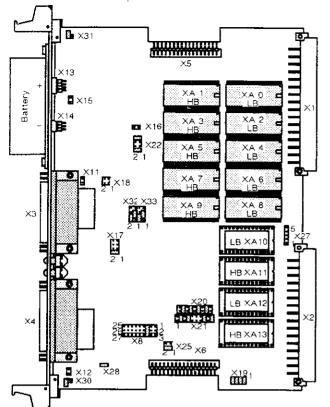

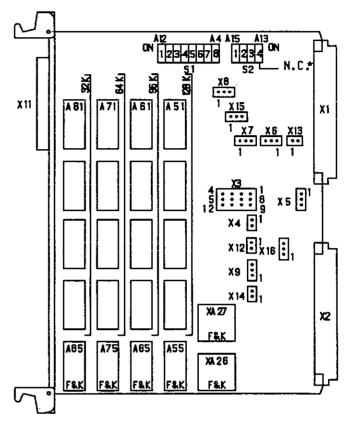

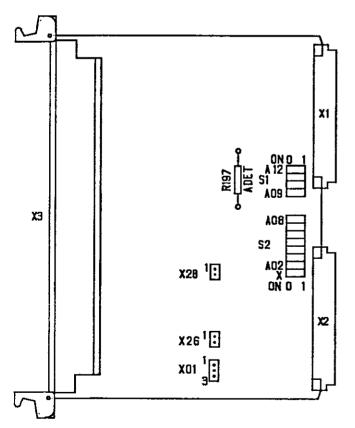

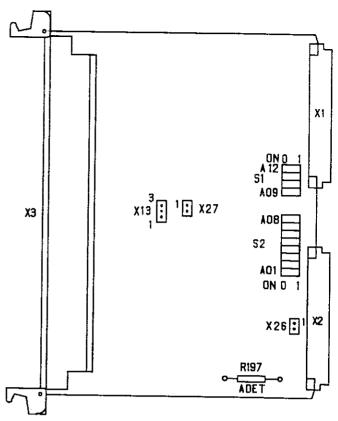

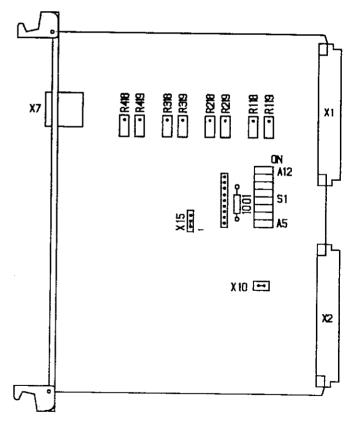

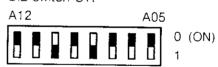

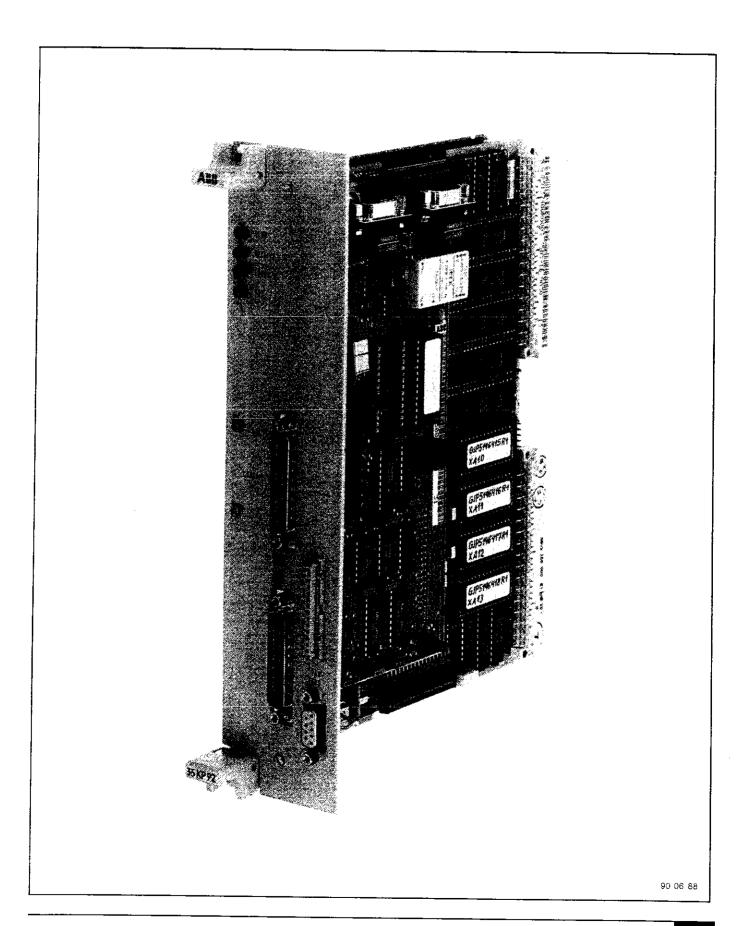

Fig. 5.1-2 Component side (top view)

| Code       | Interface, plug                                              | Design                                       | Pole         |

|------------|--------------------------------------------------------------|----------------------------------------------|--------------|

| X 1        | MPST-Bus                                                     | DIN41612, Part 2<br>constr. form C           | 32           |

| X 2        | MPST-Bus                                                     | DIN41612, Part 2<br>constr. form C           | 32           |

| × 3        | Interrupt, clock,<br>I/O port, T300                          | Wire-Wrap                                    | 34           |

|            | signals<br>Size of the transfer<br>memory                    | Jumper field                                 | 3            |

| X 5        | RAM/EPROM                                                    | Wire-Wrap                                    | 18           |

| X 6        | equipment<br>CCU or an active<br>subscriber                  | Jumper field                                 | 2            |

| X 9<br>X11 | Wait states<br>Subscriber number<br>System bus (to           | Jumper field<br>Jumper field<br>Ribbon cable | 2<br>8<br>34 |

| X12        | 35 DS 90, 35 DS 91)<br>System bus (to<br>35 DS 90, 35 DS 91) | Ribbon cable                                 | 34           |

## 5.1.4 Plug assignment

# 5.1.4.1 MPST bus interface, plugs X1, X2

All inputs of the interfaces X1 and X2 have a fan in of max. IiH = 0.04 mA; IiL = 1.6 mA.

All the outputs of the interfaces X1 and X2 have a fan out of max. IoH = -0.4 mA; IoL = 16 mA.

Plug X1:

| Pin    | Signal   | Meaning         | Pin    | Signal | Meaning              |

|--------|----------|-----------------|--------|--------|----------------------|

| X1. 2a | UB1      | 5 V voltage     | X1. 2c | U B1   | 5 V voltage          |

| X1. 4a | UB1      | 5 V voltage     | X1. 4c | U B1   | 5 V voltage          |

| X1.6a  | U B3     | - 15 V voltage  | X1. 6c | U B2   | 15 V voltage         |

| X1.8a  | A00      | Address bit 00  | X1. 8c | A01    | Address bit 01       |

| X1.10a | A02      | Address bit 02  | X1.10c | A03    | Address bit 03       |

| X1.12a | A04      | Address bit 04  | X1.12c | A05    | Address bit 05       |

| X1.14a | A06      | Address bit 06  | X1.14c | A07    | Address bit 07       |

| X1.16a | A08      | Address bit 08  | X1.16c | A09    | Address bit 09       |

| X1.18a | A10      | Address bit 10  | X1.18c | A11    | Address bit 11       |

| X1.20a | A12      | Address bit 12  | X1.20c | A13    | Address bit 13       |

| X1.22a | A14      | Address bit 14  | X1.22c | A15    | Address bit 15       |

| X1.24a | WO       | Word transfer   | X1.24c | PFD    | Power Failure Detect |

| X1.26a | <u> </u> |                 | X1.26c | -      | -                    |

| X1.28a | BB       | Bus Busy        | X1.28c | RBB    | Reset Bus Busy       |

| X1.30a | SRQ      | Service Request | X1.30c | HSRQ   | Hold Status SRQ      |

| X1.32a | ACKo     | Acknowledge out | X1.32c | ACKi   | Acknowledge in       |

Plug X2:

| Pin    | Signal     | Meaning                | Pin    | Signal | Meaning         |

|--------|------------|------------------------|--------|--------|-----------------|

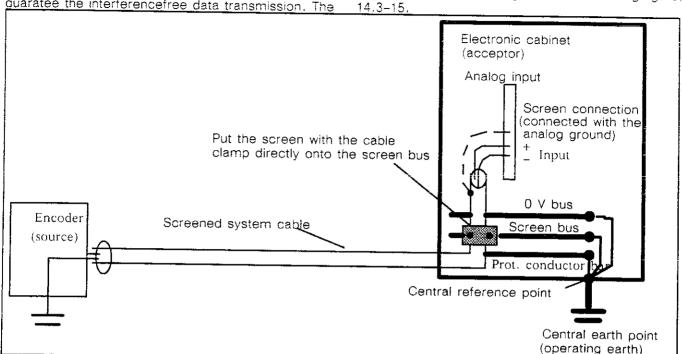

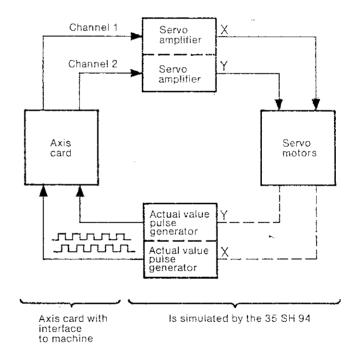

| X2. 2a | D00        | Data bit 00            | X2. 2c | D01    | Data bit 01     |